mirror of

https://github.com/Domipheus/RPU.git

synced 2025-04-18 19:15:13 -04:00

Rearrange readme and add overview image.

This commit is contained in:

parent

439781c194

commit

9f24beba69

1 changed files with 7 additions and 3 deletions

10

README.md

10

README.md

|

|

@ -3,8 +3,12 @@ Basic RISC-V CPU implementation in VHDL.

|

|||

|

||||

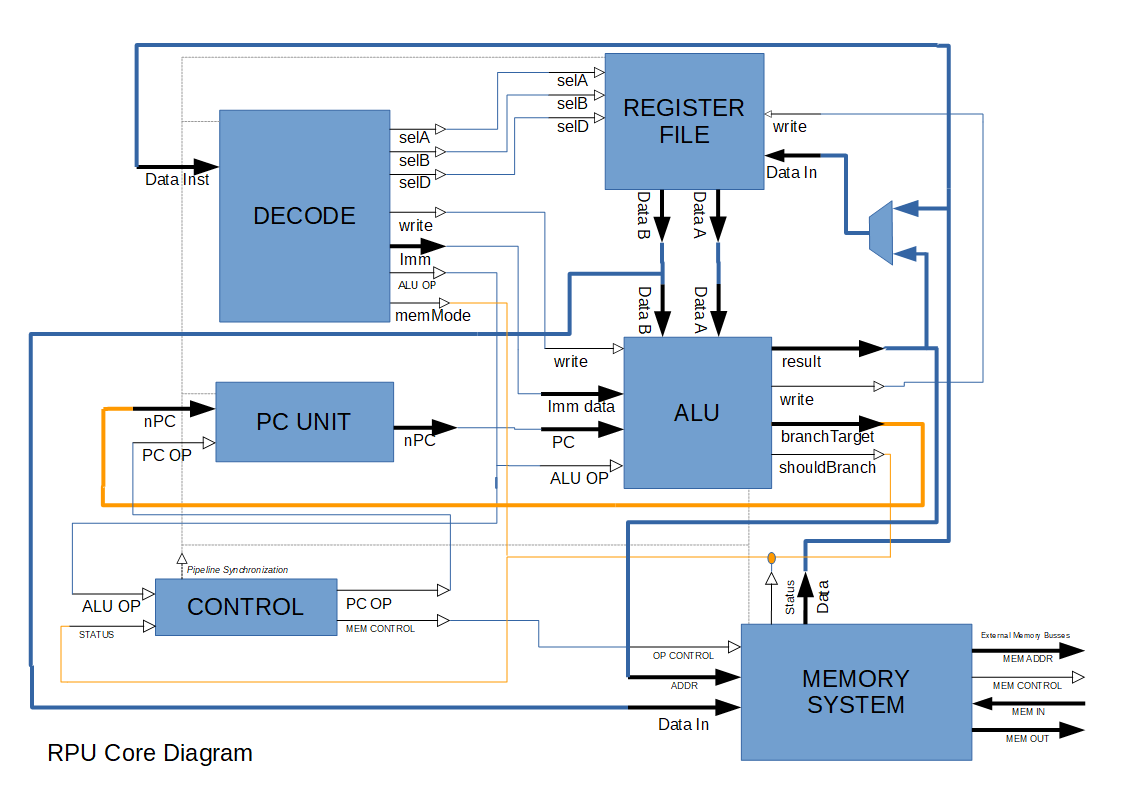

This is a RV32I ISA CPU implementation, based off of my TPU CPU design. It is very simple, is missing several features, but can run rv32i-compiled GCC toolchain binaries at over 200MHz on a Digilent Arty S7-50 board, built with Xilinx Spartan 7 tools.

|

||||

|

||||

Please let me know if you are using any of the RPU design in your own projects! I am contactable on twitter @domipheus.

|

||||

|

||||

# Implementation

|

||||

|

||||

|

||||

|

||||

Implementation detail is written about via blogs available at http://labs.domipheus.com/blog/designing-a-cpu-in-vhdl-part-15-introducing-rpu/

|

||||

|

||||

The tests in the repo are incredibly old and basic, and included only as a baseline to help. They will be expanded upon in time.

|

||||

|

||||

Please let me know if you are using any of the RPU design in your own projects! I am contactable on twitter @domipheus.

|

||||

The tests in the repo are incredibly old and basic, and included only as a baseline to help. They will be expanded upon in time.

|

||||

Loading…

Add table

Reference in a new issue