mirror of

https://github.com/openhwgroup/cva6.git

synced 2025-04-20 04:07:36 -04:00

Enable D$ by default and extend README

This commit is contained in:

parent

1d173b3742

commit

99a2fae447

5 changed files with 54 additions and 35 deletions

51

README.md

51

README.md

|

|

@ -83,25 +83,65 @@ $ make sim riscv-test-dir=$RISCV/riscv64-unknown-elf/bin riscv-test=pk target-op

|

|||

|

||||

## FPGA Emulation

|

||||

|

||||

We provide support for the [Genesys 2 board](https://reference.digilentinc.com/reference/programmable-logic/genesys-2/reference-manual).

|

||||

We currently provide support for the [Genesys 2 board](https://reference.digilentinc.com/reference/programmable-logic/genesys-2/reference-manual).

|

||||

|

||||

During Synthesis set the following tick defines need to be set:

|

||||

|

||||

```

|

||||

FPGA_TARGET_XILINX

|

||||

GENESYSII

|

||||

```

|

||||

|

||||

TBD: FPGA flow

|

||||

|

||||

Default baudrate is `9600`:

|

||||

Default baudrate is `115200`:

|

||||

```

|

||||

$ screen /dev/ttyUSB0 9600

|

||||

$ screen /dev/ttyUSB0 115200

|

||||

```

|

||||

|

||||

### Debugging

|

||||

|

||||

[OpenOCD](http://openocd.org/doc/html/Architecture-and-Core-Commands.html)

|

||||

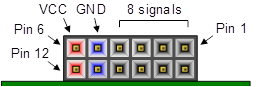

You can debug (and program) the FPGA using [OpenOCD](http://openocd.org/doc/html/Architecture-and-Core-Commands.html). We provide two example scripts for OpenOCD, both to be used with Olimex Debug adapter. The JTAG port ist mapped to PMOD `JC` on the Gensys 2 board. You will need to connect the following wires to your debug adapter:

|

||||

|

||||

|

||||

|

||||

| Pin | Nr. |

|

||||

|----------|-----|

|

||||

| `tck` | JC1 |

|

||||

| `tdi` | JC2 |

|

||||

| `tdo` | JC3 |

|

||||

| `tms` | JC4 |

|

||||

| `trst_n` | JC7 |

|

||||

|

||||

|

||||

```

|

||||

$ openocd -f fpga/ariane_tiny.cfg

|

||||

Open On-Chip Debugger 0.10.0+dev-00195-g933cb87 (2018-09-14-19:32)

|

||||

Licensed under GNU GPL v2

|

||||

For bug reports, read

|

||||

http://openocd.org/doc/doxygen/bugs.html

|

||||

adapter speed: 1000 kHz

|

||||

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

|

||||

Info : clock speed 1000 kHz

|

||||

Info : TAP riscv.cpu does not have IDCODE

|

||||

Info : datacount=2 progbufsize=12

|

||||

Info : Examined RISC-V core; found 1 harts

|

||||

Info : hart 0: XLEN=64, misa=0x8000000000141105

|

||||

Info : Listening on port 3333 for gdb connections

|

||||

Ready for Remote Connections

|

||||

Info : Listening on port 6666 for tcl connections

|

||||

Info : Listening on port 4444 for telnet connections

|

||||

Info : accepting 'gdb' connection on tcp/3333

|

||||

```

|

||||

|

||||

Then you will be able to either connect through `telnet` or with `gdb`:

|

||||

|

||||

```

|

||||

$ riscv64-unknown-elf-gdb /path/to/elf

|

||||

(gdb) target remote localhost:3333

|

||||

(gdb) load

|

||||

Loading section .text, size 0x6508 lma 0x80000000

|

||||

Loading section .rodata, size 0x900 lma 0x80006508

|

||||

(gdb) b putchar

|

||||

(gdb) c

|

||||

Continuing.

|

||||

|

|

@ -186,7 +226,7 @@ $ make

|

|||

$ [sudo] make install

|

||||

```

|

||||

|

||||

### Tandem Verification with Spike

|

||||

<!-- ### Tandem Verification with Spike

|

||||

|

||||

```

|

||||

$ make sim preload=/home/zarubaf/Downloads/riscv-tests/build/benchmarks/dhrystone.riscv tandem=1

|

||||

|

|

@ -200,6 +240,7 @@ There are a couple of caveats:

|

|||

- The RTC clock needs to be sufficiently slow (e.g.: 32 kHz seems to work). This is needed as otherwise there will be a difference when reading the `mtime` register as the RTL simulation takes more time to propagate the information through the system.

|

||||

- All traps except memory traps need to zero the `tval` register. There is a switch you can set in `ariane_pkg`.

|

||||

- `mcycle` needs to be incremented with `instret` to be similar to the performance counters found in Spike (IPC = 1)

|

||||

-->

|

||||

|

||||

### Re-generating the Bootcode (ZSBL)

|

||||

|

||||

|

|

|

|||

|

|

@ -8,7 +8,7 @@

|

|||

// CONDITIONS OF ANY KIND, either express or implied. See the License for the

|

||||

// specific language governing permissions and limitations under the License.

|

||||

|

||||

// Top-level for Genesys 2

|

||||

// Xilinx FPGA top-level

|

||||

module ariane_xilinx (

|

||||

`ifdef VCU118

|

||||

input wire c0_sys_clk_p , // 250 MHz Clock for DDR

|

||||

|

|

@ -170,29 +170,6 @@ assign ndmreset_n = ~ndmreset ;

|

|||

|

||||

logic [NBSlave-1:0] pc_asserted;

|

||||

|

||||

// ila_0 i_ila_0 (

|

||||

// .clk(clk), // input wire clk

|

||||

// .probe0(tck), // input wire [63:0] probe0

|

||||

// .probe1(tdo), // input wire [63:0] probe1

|

||||

// .probe2(tdi), // input wire [0:0] probe2

|

||||

// .probe3(tms), // input wire [0:0] probe3

|

||||

// .probe4(trst_n), // input wire [0:0] probe4

|

||||

// .probe5(ndmreset), // input wire [1:0] probe5

|

||||

// .probe6(rst_n), // input wire [0:0] probe6

|

||||

// .probe7(cpu_reset), // input wire [0:0] probe7

|

||||

// .probe8(1'b0), // input wire [0:0] probe8

|

||||

// .probe9(slave_slice[3].aw_addr), // input wire [0:0] probe10

|

||||

// .probe10(slave_slice[3].aw_valid), // input wire [0:0] probe11

|

||||

// .probe11(slave_slice[3].aw_ready), // input wire [0:0] probe12

|

||||

// .probe12(pcie_axi_araddr), // input wire [0:0] probe13

|

||||

// .probe13(pcie_axi_arvalid), // input wire [0:0] probe14

|

||||

// .probe14(pcie_axi_arready),

|

||||

// .probe15(rtc),

|

||||

// .probe16(debug_req_valid),

|

||||

// .probe17(debug_req_ready),

|

||||

// .probe18(debug_req)

|

||||

// );

|

||||

|

||||

// Slice the AXI Masters (slave ports on the XBar)

|

||||

for (genvar i = 0; i < NBSlave; i++) begin : slave_cut_gen

|

||||

axi_cut #(

|

||||

|

|

|

|||

|

|

@ -67,7 +67,7 @@

|

|||

current-speed = <115200>;

|

||||

interrupt-parent = <&PLIC0>;

|

||||

interrupts = <1>;

|

||||

reg-shift = <2>; //regs are spaced on 32 bit boundary

|

||||

reg-shift = <2>; // regs are spaced on 32 bit boundary

|

||||

reg-io-width = <4>; // only 32-bit access are supported

|

||||

};

|

||||

// xlnx_axi_ethernetlite: ethernet@12000000 {

|

||||

|

|

|

|||

|

|

@ -60,6 +60,7 @@ package ariane_pkg;

|

|||

|

||||

// enables a commit log which matches spikes commit log format for easier trace comparison

|

||||

localparam bit ENABLE_SPIKE_COMMIT_LOG = 1'b0;

|

||||

|

||||

// ------------- Dangerouse -------------

|

||||

// if set to zero a flush will not invalidate the cache-lines, in a single core environment

|

||||

// where coherence is not necessary this can improve performance. This needs to be switched on

|

||||

|

|

@ -67,11 +68,11 @@ package ariane_pkg;

|

|||

localparam logic INVALIDATE_ON_FLUSH = 1'b1;

|

||||

// enable performance cycle counter, if set to zero mcycle will be incremented

|

||||

// with instret (non RISC-V conformal)

|

||||

localparam bit ENABLE_CYCLE_COUNT = 1'b0;

|

||||

localparam bit ENABLE_CYCLE_COUNT = 1'b1;

|

||||

// mark WIF as nop

|

||||

localparam bit ENABLE_WFI = 1'b0;

|

||||

// this is Spike behaviour

|

||||

localparam bit ZERO_TVAL = 1'b1;

|

||||

localparam bit ENABLE_WFI = 1'b1;

|

||||

// Spike zeros tval on all exception except memory faults

|

||||

localparam bit ZERO_TVAL = 1'b0;

|

||||

|

||||

// read mask for SSTATUS over MMSTATUS

|

||||

localparam logic [63:0] SMODE_STATUS_READ_MASK = riscv::SSTATUS_UIE

|

||||

|

|

|

|||

|

|

@ -924,7 +924,7 @@ module csr_regfile #(

|

|||

mcause_q <= 64'b0;

|

||||

mscratch_q <= 64'b0;

|

||||

mtval_q <= 64'b0;

|

||||

dcache_q <= 64'b0;

|

||||

dcache_q <= 64'b1;

|

||||

icache_q <= 64'b1;

|

||||

// supervisor mode registers

|

||||

sepc_q <= 64'b0;

|

||||

|

|

|

|||

Loading…

Add table

Add a link

Reference in a new issue