mirror of

https://github.com/openhwgroup/cva6.git

synced 2025-04-20 12:17:19 -04:00

Merge pull request #167 from msfschaffner/master

Switch JTAG from PMOD to FTDI chip, update OpenPiton file list and OpenOCD cfg files.

This commit is contained in:

commit

5d3260196b

7 changed files with 101 additions and 33 deletions

|

|

@ -6,6 +6,12 @@ and this project adheres to [Semantic Versioning](http://semver.org/spec/v2.0.0.

|

|||

|

||||

## [Unreleased]

|

||||

|

||||

### Added

|

||||

|

||||

### Changed

|

||||

|

||||

- Rerouted the JTAG from PMOD to second channel of FTDI 2232 chip on Genesys 2 board

|

||||

|

||||

### 4.0.0

|

||||

|

||||

### Added

|

||||

|

|

|

|||

|

|

@ -131,9 +131,9 @@ src/debug/dmi_cdc.sv

|

|||

src/debug/dmi_jtag.sv

|

||||

src/debug/dm_sba.sv

|

||||

src/debug/dmi_jtag_tap.sv

|

||||

src/debug/debug_rom/debug_rom.sv

|

||||

openpiton/ariane_verilog_wrap.sv

|

||||

openpiton/serpent_peripherals.sv

|

||||

openpiton/debug_rom/debug_rom.sv

|

||||

bootrom/bootrom.sv

|

||||

src/plic/plic.sv

|

||||

src/plic/plic_claim_complete_tracker.sv

|

||||

|

|

|

|||

32

README.md

32

README.md

|

|

@ -157,21 +157,25 @@ This will produce a bitstream file and memory configuration file (in `fpga/work-

|

|||

|

||||

### Debugging

|

||||

|

||||

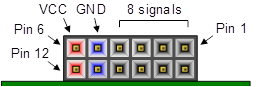

You can debug (and program) the FPGA using [OpenOCD](http://openocd.org/doc/html/Architecture-and-Core-Commands.html). We provide two example scripts for OpenOCD, both to be used with Olimex Debug adapter. The JTAG port is mapped to PMOD `JC` on the Genesys 2 board. You will need to connect the following wires to your debug adapter:

|

||||

You can debug (and program) the FPGA using [OpenOCD](http://openocd.org/doc/html/Architecture-and-Core-Commands.html). We provide two example scripts for OpenOCD below.

|

||||

|

||||

|

||||

To get started, connect the micro USB port that is labeled with JTAG to your machine. This port is attached to the FTDI 2232 USB-to-serial chip on the Genesys 2 board, and is usually used to access the native JTAG interface of the Kintex-7 FPGA (e.g. to program the device using Vivado). However, the FTDI chip also exposes a second serial link that is routed to GPIO pins on the FPGA, and we leverage this to wire up the JTAG from the RISC-V debug module.

|

||||

|

||||

| Pin | Nr. |

|

||||

|----------|-----|

|

||||

| `tck` | JC1 |

|

||||

| `tdi` | JC2 |

|

||||

| `tdo` | JC3 |

|

||||

| `tms` | JC4 |

|

||||

| `trst_n` | JC7 |

|

||||

>If you are on an Ubuntu based system you need to add the following udev rule to `/etc/udev/rules.d/99-ftdi.rules`

|

||||

>```

|

||||

> SUBSYSTEM=="usb", ACTION=="add", ATTRS{idProduct}=="6010", ATTRS{idVendor}=="0403", MODE="664", GROUP="plugdev"

|

||||

>```

|

||||

|

||||

Once attached to your system, the FTDI chip should be listed when you type `lsusb`

|

||||

|

||||

```

|

||||

$ openocd -f fpga/ariane_tiny.cfg

|

||||

Bus 005 Device 019: ID 0403:6010 Future Technology Devices International, Ltd FT2232C/D/H Dual UART/FIFO IC

|

||||

```

|

||||

|

||||

If this is the case, you can go on and start openocd with the `fpga/ariane.cfg` configuration file:

|

||||

|

||||

```

|

||||

$ openocd -f fpga/ariane.cfg

|

||||

Open On-Chip Debugger 0.10.0+dev-00195-g933cb87 (2018-09-14-19:32)

|

||||

Licensed under GNU GPL v2

|

||||

For bug reports, read

|

||||

|

|

@ -180,7 +184,7 @@ adapter speed: 1000 kHz

|

|||

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

|

||||

Info : clock speed 1000 kHz

|

||||

Info : TAP riscv.cpu does not have IDCODE

|

||||

Info : datacount=2 progbufsize=12

|

||||

Info : datacount=2 progbufsize=8

|

||||

Info : Examined RISC-V core; found 1 harts

|

||||

Info : hart 0: XLEN=64, misa=0x8000000000141105

|

||||

Info : Listening on port 3333 for gdb connections

|

||||

|

|

@ -219,12 +223,6 @@ You can read or write device memory by using:

|

|||

(gdb) set $pc = 0x1000

|

||||

```

|

||||

|

||||

If you are on an Ubuntu based system you need to add the following udev rule to `/etc/udev/rules.d/olimex-arm-usb-tiny-h.rules`

|

||||

|

||||

>```

|

||||

> SUBSYSTEM=="usb", ACTION=="add", ATTRS{idProduct}=="002a", ATTRS{idVendor}=="15ba", MODE="664", GROUP="plugdev"

|

||||

>```

|

||||

|

||||

### Preliminary Support for OpenPiton Cache System

|

||||

|

||||

Ariane has preliminary support for the OpenPiton distributed cache system from Princeton University. To this end, a different L1 cache subsystem (`src/cache_subsystem/serpent_cache_subsystem.sv`) has been developed that follows a write-through protocol and that has support for cache invalidations and atomics.

|

||||

|

|

|

|||

|

|

@ -1,13 +1,24 @@

|

|||

adapter_khz 1000

|

||||

|

||||

interface ftdi

|

||||

# ftdi_device_desc "Olimex Ltd. ARM-USB-OCD-H JTAG+RS232"

|

||||

ftdi_vid_pid 0x15ba 0x002b

|

||||

ftdi_vid_pid 0x0403 0x6010

|

||||

|

||||

ftdi_layout_init 0x0808 0x0a1b

|

||||

ftdi_layout_signal nSRST -oe 0x0200

|

||||

ftdi_layout_signal nTRST -data 0x0100 -oe 0x0100

|

||||

ftdi_layout_signal LED -data 0x0800

|

||||

# Channel 1 is taken by Xilinx JTAG

|

||||

ftdi_channel 0

|

||||

|

||||

# links:

|

||||

# http://openocd.org/doc-release/html/Debug-Adapter-Configuration.html

|

||||

#

|

||||

# Bit MPSSE FT2232 JTAG Type Description

|

||||

# Bit0 TCK ADBUS0 TCK Out Clock Signal Output

|

||||

# Bit1 TDI ADBUS1 TDI Out Serial Data Out

|

||||

# Bit2 TDO ADBUS2 TDO In Serial Data In

|

||||

# Bit3 TMS ADBUS3 TMS Out Select Signal Out

|

||||

# Bit4 GPIOL0 ADBUS4 nTRST In/Out General Purpose I/O

|

||||

# this corresponds to the following in/out layout, with TMS initially set to 1

|

||||

ftdi_layout_init 0x0018 0x001b

|

||||

# we only have to specify nTRST, the others are assigned correctly by default

|

||||

ftdi_layout_signal nTRST -ndata 0x0010

|

||||

|

||||

set _CHIPNAME riscv

|

||||

jtag newtap $_CHIPNAME cpu -irlen 5

|

||||

|

|

|

|||

30

fpga/ariane_pmod.cfg

Normal file

30

fpga/ariane_pmod.cfg

Normal file

|

|

@ -0,0 +1,30 @@

|

|||

adapter_khz 1000

|

||||

|

||||

interface ftdi

|

||||

# ftdi_device_desc "Olimex Ltd. ARM-USB-OCD-H JTAG+RS232"

|

||||

ftdi_vid_pid 0x15ba 0x002b

|

||||

|

||||

ftdi_layout_init 0x0808 0x0a1b

|

||||

ftdi_layout_signal nSRST -oe 0x0200

|

||||

ftdi_layout_signal nTRST -data 0x0100 -oe 0x0100

|

||||

ftdi_layout_signal LED -data 0x0800

|

||||

|

||||

set _CHIPNAME riscv

|

||||

jtag newtap $_CHIPNAME cpu -irlen 5

|

||||

|

||||

set _TARGETNAME $_CHIPNAME.cpu

|

||||

# select the HART to debug with the coreid switch

|

||||

target create $_TARGETNAME riscv -chain-position $_TARGETNAME -coreid 0

|

||||

|

||||

gdb_report_data_abort enable

|

||||

gdb_report_register_access_error enable

|

||||

|

||||

riscv set_reset_timeout_sec 120

|

||||

riscv set_command_timeout_sec 120

|

||||

|

||||

# prefer to use sba for system bus access

|

||||

riscv set_prefer_sba off

|

||||

|

||||

init

|

||||

halt

|

||||

echo "Ready for Remote Connections"

|

||||

|

|

@ -13,7 +13,8 @@ set _CHIPNAME riscv

|

|||

jtag newtap $_CHIPNAME cpu -irlen 5

|

||||

|

||||

set _TARGETNAME $_CHIPNAME.cpu

|

||||

target create $_TARGETNAME riscv -chain-position $_TARGETNAME

|

||||

# select the HART to debug with the coreid switch

|

||||

target create $_TARGETNAME riscv -chain-position $_TARGETNAME -coreid 0

|

||||

|

||||

gdb_report_data_abort enable

|

||||

gdb_report_register_access_error enable

|

||||

|

|

@ -1,19 +1,27 @@

|

|||

\## Buttons

|

||||

## Buttons

|

||||

set_property -dict {PACKAGE_PIN R19 IOSTANDARD LVCMOS33} [get_ports cpu_resetn]

|

||||

|

||||

## PMOD Header JC

|

||||

set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports tck]

|

||||

set_property -dict {PACKAGE_PIN AJ27 IOSTANDARD LVCMOS33} [get_ports tdi]

|

||||

set_property -dict {PACKAGE_PIN AH30 IOSTANDARD LVCMOS33} [get_ports tdo]

|

||||

set_property -dict {PACKAGE_PIN AK29 IOSTANDARD LVCMOS33} [get_ports tms]

|

||||

set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports trst_n]

|

||||

# set_property -dict {PACKAGE_PIN AC26 IOSTANDARD LVCMOS33} [get_ports tck]

|

||||

# set_property -dict {PACKAGE_PIN AJ27 IOSTANDARD LVCMOS33} [get_ports tdi]

|

||||

# set_property -dict {PACKAGE_PIN AH30 IOSTANDARD LVCMOS33} [get_ports tdo]

|

||||

# set_property -dict {PACKAGE_PIN AK29 IOSTANDARD LVCMOS33} [get_ports tms]

|

||||

# set_property -dict {PACKAGE_PIN AD26 IOSTANDARD LVCMOS33} [get_ports trst_n]

|

||||

# accept sub-optimal placement

|

||||

# set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets tck_IBUF]

|

||||

|

||||

|

||||

## To use FTDI FT2232 JTAG

|

||||

set_property -dict { PACKAGE_PIN Y29 IOSTANDARD LVCMOS33 } [get_ports { trst_n }];

|

||||

set_property -dict { PACKAGE_PIN AD27 IOSTANDARD LVCMOS33 } [get_ports { tck }];

|

||||

set_property -dict { PACKAGE_PIN W27 IOSTANDARD LVCMOS33 } [get_ports { tdi }];

|

||||

set_property -dict { PACKAGE_PIN W28 IOSTANDARD LVCMOS33 } [get_ports { tdo }];

|

||||

set_property -dict { PACKAGE_PIN W29 IOSTANDARD LVCMOS33 } [get_ports { tms }];

|

||||

|

||||

## UART

|

||||

set_property -dict {PACKAGE_PIN Y23 IOSTANDARD LVCMOS33} [get_ports tx]

|

||||

set_property -dict {PACKAGE_PIN Y20 IOSTANDARD LVCMOS33} [get_ports rx]

|

||||

|

||||

# accept sub-optimal placement

|

||||

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets tck_IBUF]

|

||||

|

||||

## LEDs

|

||||

set_property -dict {PACKAGE_PIN T28 IOSTANDARD LVCMOS33} [get_ports {led[0]}]

|

||||

|

|

@ -69,6 +77,7 @@ create_clock -period 40.000 -name eth_rxck_virt

|

|||

# conservatively assuming +/- 2ns skew of rxd/rxctl

|

||||

create_clock -period 40.000 -name eth_rxck -waveform {2.000 22.000} [get_ports eth_rxck]

|

||||

|

||||

|

||||

# Input constraints

|

||||

set_input_delay -clock [get_clocks eth_rxck_virt] -min -add_delay 0.000 [get_ports {eth_rxd[*]}]

|

||||

set_input_delay -clock [get_clocks eth_rxck_virt] -max -add_delay 4.000 [get_ports {eth_rxd[*]}]

|

||||

|

|

@ -92,3 +101,16 @@ set_property -dict {PACKAGE_PIN R29 IOSTANDARD LVCMOS33} [get_ports spi_mosi]

|

|||

|

||||

# Genesys 2 has a quad SPI flash

|

||||

set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

|

||||

|

||||

## JTAG

|

||||

# minimize routing delay

|

||||

set_max_delay -to [get_ports { td } ] 5

|

||||

set_max_delay -from [get_ports { tms } ] 5

|

||||

set_max_delay -from [get_ports { trst_n } ] 5

|

||||

|

||||

# reset signal

|

||||

set_false_path -from [get_ports { trst_n } ]

|

||||

|

||||

# constrain clock domain crossing

|

||||

set_false_path -from [get_clocks tck] -to [get_clocks clk_out1]

|

||||

set_max_delay -from [get_clocks tck] -to [get_clocks clk_out1] 5

|

||||

|

|

|

|||

Loading…

Add table

Add a link

Reference in a new issue