mirror of

https://github.com/openhwgroup/cva6.git

synced 2025-04-22 13:17:41 -04:00

Merge pull request #135 from pulp-platform/fpga_dev

WIP: Merge FPGA changes

This commit is contained in:

commit

f8692af1a5

117 changed files with 10018 additions and 2828 deletions

|

|

@ -6,8 +6,8 @@ root = true

|

|||

end_of_line = lf

|

||||

insert_final_newline = true

|

||||

trim_trailing_whitespace = true

|

||||

max_line_length = off

|

||||

max_line_length = 100

|

||||

# 4 space indentation

|

||||

[*.{sv, svh, v, vhd}]

|

||||

indent_style = space

|

||||

indent_size = 4

|

||||

indent_size = 2

|

||||

|

|

|

|||

8

.gitignore

vendored

8

.gitignore

vendored

|

|

@ -22,4 +22,12 @@ build/

|

|||

*.vcd

|

||||

*.log

|

||||

*.out

|

||||

*.jou

|

||||

*.o

|

||||

uart

|

||||

work-ver/*

|

||||

fpga/work-fpga

|

||||

stdout/

|

||||

work-dpi/

|

||||

tb/riscv-isa-sim/

|

||||

work-*/*

|

||||

|

|

|

|||

15

.gitmodules

vendored

15

.gitmodules

vendored

|

|

@ -13,6 +13,21 @@

|

|||

[submodule "src/axi"]

|

||||

path = src/axi

|

||||

url = https://github.com/pulp-platform/axi.git

|

||||

[submodule "src/register_interface"]

|

||||

path = src/register_interface

|

||||

url = https://github.com/pulp-platform/register_interface.git

|

||||

[submodule "fpga/src/apb_uart"]

|

||||

path = fpga/src/apb_uart

|

||||

url = https://github.com/pulp-platform/apb_uart.git

|

||||

[submodule "fpga/src/apb_node"]

|

||||

path = fpga/src/apb_node

|

||||

url = https://github.com/pulp-platform/apb_node.git

|

||||

[submodule "fpga/src/axi2apb"]

|

||||

path = fpga/src/axi2apb

|

||||

url = https://github.com/pulp-platform/axi2apb.git

|

||||

[submodule "fpga/src/axi_slice"]

|

||||

path = fpga/src/axi_slice

|

||||

url = https://github.com/pulp-platform/axi_slice.git

|

||||

[submodule "src/fpu_div_sqrt_mvp"]

|

||||

path = src/fpu_div_sqrt_mvp

|

||||

url = https://github.com/pulp-platform/fpu_div_sqrt_mvp.git

|

||||

|

|

|

|||

106

Makefile

Executable file → Normal file

106

Makefile

Executable file → Normal file

|

|

@ -28,7 +28,9 @@ test-location ?= output/test

|

|||

torture-logs :=

|

||||

# custom elf bin to run with sim or sim-verilator

|

||||

elf-bin ?= tmp/riscv-tests/build/benchmarks/dhrystone.riscv

|

||||

|

||||

# root path

|

||||

mkfile_path := $(abspath $(lastword $(MAKEFILE_LIST)))

|

||||

root-dir := $(dir $(mkfile_path))

|

||||

|

||||

# Sources

|

||||

# Package files -> compile first

|

||||

|

|

@ -37,13 +39,16 @@ ariane_pkg := include/riscv_pkg.sv \

|

|||

include/ariane_pkg.sv \

|

||||

include/std_cache_pkg.sv \

|

||||

src/axi/src/axi_pkg.sv \

|

||||

src/register_interface/src/reg_intf.sv \

|

||||

include/axi_intf.sv \

|

||||

tb/ariane_soc_pkg.sv \

|

||||

include/ariane_axi_pkg.sv \

|

||||

src/fpu/src/pkg/fpnew_pkg.vhd \

|

||||

src/fpu/src/pkg/fpnew_fmts_pkg.vhd \

|

||||

src/fpu/src/pkg/fpnew_comps_pkg.vhd \

|

||||

src/fpu_div_sqrt_mvp/hdl/defs_div_sqrt_mvp.sv \

|

||||

src/fpu/src/pkg/fpnew_pkg_constants.vhd

|

||||

ariane_pkg := $(addprefix $(root-dir), $(ariane_pkg))

|

||||

|

||||

# utility modules

|

||||

util := $(wildcard src/util/*.svh) \

|

||||

|

|

@ -51,13 +56,18 @@ util := $(wildcard src/util/*.svh) \

|

|||

src/util/instruction_tracer_if.sv \

|

||||

src/tech_cells_generic/src/cluster_clock_gating.sv \

|

||||

src/util/sram.sv

|

||||

|

||||

util := $(addprefix $(root-dir), $(util))

|

||||

# Test packages

|

||||

test_pkg := $(wildcard tb/test/*/*sequence_pkg.sv*) \

|

||||

$(wildcard tb/test/*/*_pkg.sv*)

|

||||

# DPI

|

||||

dpi := $(patsubst tb/dpi/%.cc,${dpi-library}/%.o,$(wildcard tb/dpi/*.cc))

|

||||

dpi_hdr := $(wildcard tb/dpi/*.h)

|

||||

dpi_hdr := $(addprefix $(root-dir), $(dpi_hdr))

|

||||

CFLAGS := -I$(QUESTASIM_HOME)/include \

|

||||

-Itb/riscv-isa-sim/install/include/spike \

|

||||

-std=c++11 -I../tb/dpi

|

||||

|

||||

# this list contains the standalone components

|

||||

src := $(filter-out src/ariane_regfile.sv, $(wildcard src/*.sv)) \

|

||||

$(wildcard src/fpu/src/utils/*.vhd) \

|

||||

|

|

@ -66,13 +76,19 @@ src := $(filter-out src/ariane_regfile.sv, $(wildcard src/*.sv)) \

|

|||

$(filter-out src/fpu_div_sqrt_mvp/hdl/defs_div_sqrt_mvp.sv, \

|

||||

$(wildcard src/fpu_div_sqrt_mvp/hdl/*.sv)) \

|

||||

$(wildcard src/frontend/*.sv) \

|

||||

$(wildcard src/cache_subsystem/*.sv) \

|

||||

$(filter-out src/cache_subsystem/std_no_dcache.sv, \

|

||||

$(wildcard src/cache_subsystem/*.sv)) \

|

||||

$(wildcard bootrom/*.sv) \

|

||||

$(wildcard src/clint/*.sv) \

|

||||

$(wildcard fpga/src/axi2apb/src/*.sv) \

|

||||

$(wildcard fpga/src/axi_slice/src/*.sv) \

|

||||

$(wildcard src/plic/*.sv) \

|

||||

$(wildcard src/axi_node/src/*.sv) \

|

||||

$(wildcard src/axi_mem_if/src/*.sv) \

|

||||

$(filter-out src/debug/dm_pkg.sv, $(wildcard src/debug/*.sv)) \

|

||||

$(wildcard src/debug/debug_rom/*.sv) \

|

||||

src/register_interface/src/apb_to_reg.sv \

|

||||

src/axi/src/axi_multicut.sv \

|

||||

src/fpu/src/fpnew.vhd \

|

||||

src/fpu/src/fpnew_top.vhd \

|

||||

src/common_cells/src/deprecated/generic_fifo.sv \

|

||||

|

|

@ -84,26 +100,40 @@ src := $(filter-out src/ariane_regfile.sv, $(wildcard src/*.sv)) \

|

|||

src/util/axi_connect.sv \

|

||||

src/axi/src/axi_cut.sv \

|

||||

src/axi/src/axi_join.sv \

|

||||

src/axi/src/axi_delayer.sv \

|

||||

src/axi/src/axi_to_axi_lite.sv \

|

||||

src/fpga-support/rtl/SyncSpRamBeNx64.sv \

|

||||

src/common_cells/src/sync.sv \

|

||||

src/common_cells/src/cdc_2phase.sv \

|

||||

src/common_cells/src/spill_register.sv \

|

||||

src/common_cells/src/sync_wedge.sv \

|

||||

src/common_cells/src/edge_detect.sv \

|

||||

src/common_cells/src/fifo_v3.sv \

|

||||

src/common_cells/src/fifo_v2.sv \

|

||||

src/common_cells/src/fifo_v1.sv \

|

||||

src/common_cells/src/lzc.sv \

|

||||

src/common_cells/src/rrarbiter.sv \

|

||||

src/common_cells/src/pipe_reg_simple.sv \

|

||||

src/common_cells/src/ready_valid_delay.sv \

|

||||

src/common_cells/src/lfsr_8bit.sv \

|

||||

src/common_cells/src/lfsr_16bit.sv \

|

||||

src/common_cells/src/counter.sv \

|

||||

src/common_cells/src/pipe_reg_simple.sv \

|

||||

src/tech_cells_generic/src/cluster_clock_inverter.sv \

|

||||

src/tech_cells_generic/src/pulp_clock_mux2.sv \

|

||||

tb/ariane_testharness.sv \

|

||||

tb/ariane_peripherals.sv \

|

||||

tb/common/uart.sv \

|

||||

tb/common/SimDTM.sv \

|

||||

tb/common/SimJTAG.sv

|

||||

|

||||

# root path

|

||||

root-dir := $(shell pwd)

|

||||

src := $(addprefix $(root-dir), $(src))

|

||||

|

||||

uart_src := $(wildcard fpga/src/apb_uart/src/*.vhd)

|

||||

uart_src := $(addprefix $(root-dir), $(uart_src))

|

||||

|

||||

fpga_src := $(wildcard fpga/src/*.sv) $(wildcard fpga/src/bootrom/*.sv)

|

||||

fpga_src := $(addprefix $(root-dir), $(fpga_src))

|

||||

|

||||

# look for testbenches

|

||||

tbs := tb/ariane_tb.sv tb/ariane_testharness.sv

|

||||

# RISCV asm tests and benchmark setup (used for CI)

|

||||

|

|

@ -121,16 +151,10 @@ riscv-benchmarks := $(shell xargs printf '\n%s' < $(riscv-benchmarks-li

|

|||

incdir :=

|

||||

# Compile and sim flags

|

||||

compile_flag += +cover=bcfst+/dut -incr -64 -nologo -quiet -suppress 13262 -permissive +define+$(defines)

|

||||

|

||||

compile_flag_vhd += -64 -nologo -quiet -2008

|

||||

uvm-flags += +UVM_NO_RELNOTES +UVM_VERBOSITY=LOW

|

||||

questa-flags += -t 1ns -64 -coverage -classdebug $(gui-sim) $(QUESTASIM_FLAGS)

|

||||

# if defined, calls the questa targets in batch mode

|

||||

ifdef batch-mode

|

||||

questa-flags += -c

|

||||

questa-cmd := -do "coverage save -onexit tmp/$@.ucdb; run -a; quit -code [coverage attribute -name TESTSTATUS -concise]"

|

||||

else

|

||||

questa-cmd := -do " log -r /*; run -all;"

|

||||

endif

|

||||

|

||||

# Iterate over all include directories and write them with +incdir+ prefixed

|

||||

# +incdir+ works for Verilator and QuestaSim

|

||||

|

|

@ -140,17 +164,43 @@ list_incdir := $(foreach dir, ${incdir}, +incdir+$(dir))

|

|||

riscv-torture-dir := tmp/riscv-torture

|

||||

riscv-torture-bin := java -Xmx1G -Xss8M -XX:MaxPermSize=128M -jar sbt-launch.jar

|

||||

|

||||

# if defined, calls the questa targets in batch mode

|

||||

ifdef batch-mode

|

||||

questa-flags += -c

|

||||

questa-cmd := -do "coverage save -onexit tmp/$@.ucdb; run -a; quit -code [coverage attribute -name TESTSTATUS -concise]"

|

||||

questa-cmd += -do " log -r /*; run -all;"

|

||||

else

|

||||

questa-cmd := -do " log -r /*; run -all;"

|

||||

endif

|

||||

# we want to preload the memories

|

||||

ifdef preload

|

||||

questa-cmd += +PRELOAD=$(preload)

|

||||

elf-bin = none

|

||||

# tandem verify with spike, this requires pre-loading

|

||||

ifdef tandem

|

||||

compile_flag += +define+TANDEM

|

||||

questa-cmd += -gblso tb/riscv-isa-sim/install/lib/libriscv.so

|

||||

endif

|

||||

endif

|

||||

# remote bitbang is enabled

|

||||

ifdef rbb

|

||||

questa-cmd += +jtag_rbb_enable=1

|

||||

else

|

||||

questa-cmd += +jtag_rbb_enable=0

|

||||

endif

|

||||

|

||||

# Build the TB and module using QuestaSim

|

||||

build: $(library) $(library)/.build-srcs $(library)/.build-tb $(dpi-library)/ariane_dpi.so

|

||||

# Optimize top level

|

||||

vopt$(questa_version) $(compile_flag) -work $(library) $(top_level) -o $(top_level)_optimized +acc -check_synthesis

|

||||

|

||||

# src files

|

||||

$(library)/.build-srcs: $(ariane_pkg) $(util) $(src) $(library)

|

||||

$(library)/.build-srcs: $(ariane_pkg) $(util) $(src) $(library) $(uart_src)

|

||||

vlog$(questa_version) $(compile_flag) -work $(library) $(filter %.sv,$(ariane_pkg)) $(list_incdir) -suppress 2583

|

||||

vcom$(questa_version) $(compile_flag_vhd) -work $(library) -pedanticerrors $(filter %.vhd,$(ariane_pkg))

|

||||

vlog$(questa_version) $(compile_flag) -work $(library) $(filter %.sv,$(util)) $(list_incdir) -suppress 2583

|

||||

# Suppress message that always_latch may not be checked thoroughly by QuestaSim.

|

||||

vcom$(questa_version) $(compile_flag_vhd) -work $(library) -pedanticerrors $(filter %.vhd,$(uart_src))

|

||||

vcom$(questa_version) $(compile_flag_vhd) -work $(library) -pedanticerrors $(filter %.vhd,$(src))

|

||||

vlog$(questa_version) $(compile_flag) -work $(library) -pedanticerrors $(filter %.sv,$(src)) $(list_incdir) -suppress 2583

|

||||

touch $(library)/.build-srcs

|

||||

|

|

@ -167,7 +217,7 @@ $(library):

|

|||

# compile DPIs

|

||||

$(dpi-library)/%.o: tb/dpi/%.cc $(dpi_hdr)

|

||||

mkdir -p $(dpi-library)

|

||||

$(CXX) -shared -fPIC -std=c++0x -Bsymbolic -I$(QUESTASIM_HOME)/include -o $@ $<

|

||||

$(CXX) -shared -fPIC -std=c++0x -Bsymbolic $(CFLAGS) -c $< -o $@

|

||||

|

||||

$(dpi-library)/ariane_dpi.so: $(dpi)

|

||||

mkdir -p $(dpi-library)

|

||||

|

|

@ -179,24 +229,24 @@ $(dpi-library)/ariane_dpi.so: $(dpi)

|

|||

# if you want to run in batch mode, use make <testname> batch-mode=1

|

||||

# alternatively you can call make sim elf-bin=<path/to/elf-bin> in order to load an arbitrary binary

|

||||

sim: build

|

||||

vsim${questa_version} +permissive $(questa-flags) $(questa-cmd) -lib $(library) +max-cycles=$(max_cycles) +UVM_TESTNAME=$(test_case) \

|

||||

+BASEDIR=$(riscv-test-dir) $(uvm-flags) +jtag_rbb_enable=0 -gblso $(RISCV)/lib/libfesvr.so -sv_lib $(dpi-library)/ariane_dpi \

|

||||

vsim${questa_version} +permissive $(questa-flags) $(questa-cmd) -lib $(library) +MAX_CYCLES=$(max_cycles) +UVM_TESTNAME=$(test_case) \

|

||||

+BASEDIR=$(riscv-test-dir) $(uvm-flags) $(QUESTASIM_FLAGS) -gblso $(RISCV)/lib/libfesvr.so -sv_lib $(dpi-library)/ariane_dpi \

|

||||

${top_level}_optimized +permissive-off ++$(elf-bin) ++$(target-options) | tee sim.log

|

||||

|

||||

$(riscv-asm-tests): build

|

||||

vsim${questa_version} +permissive $(questa-flags) $(questa-cmd) -lib $(library) +max-cycles=$(max_cycles) +UVM_TESTNAME=$(test_case) \

|

||||

+BASEDIR=$(riscv-test-dir) $(uvm-flags) +jtag_rbb_enable=0 -gblso $(RISCV)/lib/libfesvr.so -sv_lib $(dpi-library)/ariane_dpi \

|

||||

${top_level}_optimized +permissive-off ++$(riscv-test-dir)/$@ ++$(target-options) | tee tmp/riscv-asm-tests-$@.log

|

||||

${top_level}_optimized $(QUESTASIM_FLAGS) +permissive-off ++$(riscv-test-dir)/$@ ++$(target-options) | tee tmp/riscv-asm-tests-$@.log

|

||||

|

||||

$(riscv-amo-tests): build

|

||||

vsim${questa_version} +permissive $(questa-flags) $(questa-cmd) -lib $(library) +max-cycles=$(max_cycles) +UVM_TESTNAME=$(test_case) \

|

||||

+BASEDIR=$(riscv-test-dir) $(uvm-flags) +jtag_rbb_enable=0 -gblso $(RISCV)/lib/libfesvr.so -sv_lib $(dpi-library)/ariane_dpi \

|

||||

${top_level}_optimized +permissive-off ++$(riscv-test-dir)/$@ ++$(target-options) | tee tmp/riscv-amo-tests-$@.log

|

||||

${top_level}_optimized $(QUESTASIM_FLAGS) +permissive-off ++$(riscv-test-dir)/$@ ++$(target-options) | tee tmp/riscv-amo-tests-$@.log

|

||||

|

||||

$(riscv-benchmarks): build

|

||||

vsim${questa_version} +permissive $(questa-flags) $(questa-cmd) -lib $(library) +max-cycles=$(max_cycles) +UVM_TESTNAME=$(test_case) \

|

||||

+BASEDIR=$(riscv-benchmarks-dir) $(uvm-flags) +jtag_rbb_enable=0 -gblso $(RISCV)/lib/libfesvr.so -sv_lib $(dpi-library)/ariane_dpi \

|

||||

${top_level}_optimized +permissive-off ++$(riscv-benchmarks-dir)/$@ ++$(target-options) | tee tmp/riscv-benchmarks-$@.log

|

||||

${top_level}_optimized $(QUESTASIM_FLAGS) +permissive-off ++$(riscv-benchmarks-dir)/$@ ++$(target-options) | tee tmp/riscv-benchmarks-$@.log

|

||||

|

||||

# can use -jX to run ci tests in parallel using X processes

|

||||

run-asm-tests: $(riscv-asm-tests)

|

||||

|

|

@ -237,13 +287,15 @@ verilate_command := $(verilator)

|

|||

-Wno-style \

|

||||

-Wno-lint \

|

||||

$(if $(DEBUG),--trace-structs --trace,) \

|

||||

-LDFLAGS "-lfesvr" -CFLAGS "-std=c++11 -I../tb/dpi" -Wall --cc --vpi \

|

||||

-LDFLAGS "-lfesvr" -CFLAGS "$(CFLAGS)" -Wall --cc --vpi \

|

||||

$(list_incdir) --top-module ariane_testharness \

|

||||

--Mdir $(ver-library) -O3 \

|

||||

--exe tb/ariane_tb.cpp tb/dpi/SimDTM.cc tb/dpi/SimJTAG.cc tb/dpi/remote_bitbang.cc

|

||||

--exe tb/ariane_tb.cpp tb/dpi/SimDTM.cc tb/dpi/SimJTAG.cc \

|

||||

tb/dpi/remote_bitbang.cc tb/dpi/msim_helper.cc

|

||||

|

||||

# User Verilator, at some point in the future this will be auto-generated

|

||||

verilate:

|

||||

@echo "[Verilator] Building Model"

|

||||

$(verilate_command)

|

||||

cd $(ver-library) && $(MAKE) -j${NUM_JOBS} -f Variane_testharness.mk

|

||||

|

||||

|

|

@ -319,6 +371,16 @@ check-torture:

|

|||

grep 'All signatures match for $(test-location)' $(riscv-torture-dir)/$(test-location).log

|

||||

diff -s $(riscv-torture-dir)/$(test-location).spike.sig $(riscv-torture-dir)/$(test-location).rtlsim.sig

|

||||

|

||||

fpga: $(ariane_pkg) $(util) $(src) $(fpga_src) $(util) $(uart_src)

|

||||

@echo "[FPGA] Generate sources"

|

||||

@echo read_vhdl {$(uart_src)} > fpga/scripts/add_sources.tcl

|

||||

@echo read_verilog -sv {$(ariane_pkg)} >> fpga/scripts/add_sources.tcl

|

||||

@echo read_verilog -sv {$(util)} >> fpga/scripts/add_sources.tcl

|

||||

@echo read_verilog -sv {$(src)} >> fpga/scripts/add_sources.tcl

|

||||

@echo read_verilog -sv {$(fpga_src)} >> fpga/scripts/add_sources.tcl

|

||||

@echo "[FPGA] Generate Bitstream"

|

||||

cd fpga && make

|

||||

|

||||

clean:

|

||||

rm -rf $(riscv-torture-dir)/output/test*

|

||||

rm -rf $(library)/ $(dpi-library)/ $(ver-library)/

|

||||

|

|

|

|||

116

README.md

116

README.md

|

|

@ -76,7 +76,7 @@ $ work-ver/Variane_testharness $RISCV/riscv64-unknown-elf/bin/pk hello.elf

|

|||

|

||||

If you want to use QuestaSim to run it you can use the following command:

|

||||

```

|

||||

$ make simc riscv-test-dir=$RISCV/riscv64-unknown-elf/bin riscv-test=pk target-options=hello.elf

|

||||

$ make sim elf-bin=$RISCV/riscv64-unknown-elf/bin/pk target-options=hello.elf batch-mode=1

|

||||

```

|

||||

|

||||

> Be patient! RTL simulation is way slower than Spike. If you think that you ran into problems you can inspect the trace files.

|

||||

|

|

@ -87,7 +87,89 @@ $ make simc riscv-test-dir=$RISCV/riscv64-unknown-elf/bin riscv-test=pk target-o

|

|||

|

||||

## FPGA Emulation

|

||||

|

||||

Coming.

|

||||

We currently only provide support for the [Genesys 2 board](https://reference.digilentinc.com/reference/programmable-logic/genesys-2/reference-manual). Tested on Vivado 2018.2.

|

||||

|

||||

```

|

||||

$ source fpga/sourceme.sh

|

||||

$ make fpga

|

||||

```

|

||||

|

||||

TODO(zarubaf): Add further TODOS and simplify flow

|

||||

|

||||

Default baudrate is `115200`:

|

||||

```

|

||||

$ screen /dev/ttyUSB0 115200

|

||||

```

|

||||

|

||||

### Debugging

|

||||

|

||||

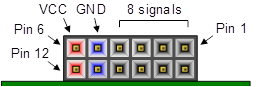

You can debug (and program) the FPGA using [OpenOCD](http://openocd.org/doc/html/Architecture-and-Core-Commands.html). We provide two example scripts for OpenOCD, both to be used with Olimex Debug adapter. The JTAG port ist mapped to PMOD `JC` on the Gensys 2 board. You will need to connect the following wires to your debug adapter:

|

||||

|

||||

|

||||

|

||||

| Pin | Nr. |

|

||||

|----------|-----|

|

||||

| `tck` | JC1 |

|

||||

| `tdi` | JC2 |

|

||||

| `tdo` | JC3 |

|

||||

| `tms` | JC4 |

|

||||

| `trst_n` | JC7 |

|

||||

|

||||

|

||||

```

|

||||

$ openocd -f fpga/ariane_tiny.cfg

|

||||

Open On-Chip Debugger 0.10.0+dev-00195-g933cb87 (2018-09-14-19:32)

|

||||

Licensed under GNU GPL v2

|

||||

For bug reports, read

|

||||

http://openocd.org/doc/doxygen/bugs.html

|

||||

adapter speed: 1000 kHz

|

||||

Info : auto-selecting first available session transport "jtag". To override use 'transport select <transport>'.

|

||||

Info : clock speed 1000 kHz

|

||||

Info : TAP riscv.cpu does not have IDCODE

|

||||

Info : datacount=2 progbufsize=12

|

||||

Info : Examined RISC-V core; found 1 harts

|

||||

Info : hart 0: XLEN=64, misa=0x8000000000141105

|

||||

Info : Listening on port 3333 for gdb connections

|

||||

Ready for Remote Connections

|

||||

Info : Listening on port 6666 for tcl connections

|

||||

Info : Listening on port 4444 for telnet connections

|

||||

Info : accepting 'gdb' connection on tcp/3333

|

||||

```

|

||||

|

||||

Then you will be able to either connect through `telnet` or with `gdb`:

|

||||

|

||||

```

|

||||

$ riscv64-unknown-elf-gdb /path/to/elf

|

||||

(gdb) target remote localhost:3333

|

||||

(gdb) load

|

||||

Loading section .text, size 0x6508 lma 0x80000000

|

||||

Loading section .rodata, size 0x900 lma 0x80006508

|

||||

(gdb) b putchar

|

||||

(gdb) c

|

||||

Continuing.

|

||||

|

||||

Program received signal SIGTRAP, Trace/breakpoint trap.

|

||||

0x0000000080009126 in putchar (s=72) at lib/qprintf.c:69

|

||||

69 uart_sendchar(s);

|

||||

(gdb) si

|

||||

0x000000008000912a 69 uart_sendchar(s);

|

||||

(gdb) p/x $mepc

|

||||

$1 = 0xfffffffffffdb5ee

|

||||

```

|

||||

|

||||

You can read or write device memory by using:

|

||||

```

|

||||

(gdb) x/i 0x1000

|

||||

0x1000: lui t0,0x4

|

||||

(gdb) set {int} 0x1000 = 22

|

||||

(gdb) set $pc = 0x1000

|

||||

```

|

||||

|

||||

If you are on an Ubuntu based system you need to add the following udev rule to `/etc/udev/rules.d/olimex-arm-usb-tiny-h.rules`

|

||||

|

||||

>```

|

||||

> SUBSYSTEM=="usb", ACTION=="add", ATTRS{idProduct}=="002a", ATTRS{idVendor}=="15ba", MODE="664", GROUP="plugdev"

|

||||

>```

|

||||

|

||||

## Planned Improvements

|

||||

|

||||

|

|

@ -99,10 +181,10 @@ The core has been developed with a full licensed version of QuestaSim. If you ha

|

|||

|

||||

To specify the test to run use (e.g.: you want to run `rv64ui-p-sraw` inside the `tmp/risc-tests/build/isa` folder:

|

||||

```

|

||||

$ make sim riscv-test=tmp/risc-tests/build/isa/rv64ui-p-sraw

|

||||

$ make sim elf-bin=path/to/rv64ui-p-sraw

|

||||

```

|

||||

|

||||

If you call `simc` instead of `sim` it will run without the GUI. QuestaSim uses `riscv-fesvr` for communication as well.

|

||||

If you call `sim` with `batch-mode=1` it will run without the GUI. QuestaSim uses `riscv-fesvr` for communication as well.

|

||||

|

||||

### CI Testsuites and Randomized Constrained Testing with Torture

|

||||

|

||||

|

|

@ -132,6 +214,7 @@ Ariane can dump a trace-log in Questa which can be easily diffed against Spike w

|

|||

```verilog

|

||||

localparam bit ENABLE_SPIKE_COMMIT_LOG = 1'b1;

|

||||

```

|

||||

This runs the randomized program on Spike and on the RTL target, and checks whether the two signatures match. The random instruction mix can be configured in the `./tmp/riscv-torture/config/default.config` file.

|

||||

This will dump a file called `trace_core_*_*_commit.log`.

|

||||

|

||||

This can be helpful for debugging long traces (e.g.: torture traces). To compile Spike with the commit log feature do:

|

||||

|

|

@ -145,7 +228,32 @@ $ make

|

|||

$ [sudo] make install

|

||||

```

|

||||

|

||||

<!-- ### Tandem Verification with Spike

|

||||

|

||||

```

|

||||

$ make sim preload=/home/zarubaf/Downloads/riscv-tests/build/benchmarks/dhrystone.riscv tandem=1

|

||||

```

|

||||

There are a couple of caveats:

|

||||

|

||||

- Memories should be initialized to zero. Random or `x` are not supported.

|

||||

- UART needs to be replaced by a mock UART which exhibits always ready behavior.

|

||||

- There is no end of test signaling at the moment. You are supposed to kill the simulation when sufficiently long run.

|

||||

- You need to use the modified Spike version in the `tb` subdirectory.

|

||||

- The RTC clock needs to be sufficiently slow (e.g.: 32 kHz seems to work). This is needed as otherwise there will be a difference when reading the `mtime` register as the RTL simulation takes more time to propagate the information through the system.

|

||||

- All traps except memory traps need to zero the `tval` register. There is a switch you can set in `ariane_pkg`.

|

||||

- `mcycle` needs to be incremented with `instret` to be similar to the performance counters found in Spike (IPC = 1)

|

||||

-->

|

||||

|

||||

### Re-generating the Bootcode (ZSBL)

|

||||

|

||||

The zero stage bootloader (ZSBL) for RTL simulation lives in `bootrom/` while the bootcode for the FPGA is in `fpga/src/bootrom`. The RTL bootcode simply jumps to the base of the DRAM where the FSBL takes over. For the FPGA the ZSBL performs additional housekeeping. Both bootloader pass the hartid as well as address to the device tree in argumen register `a0` and `a1` respectively.

|

||||

|

||||

To re-generate the bootcode you can use the existing makefile within those directories. To generate the SystemVerilog files you will need the `bitstring` python package installed on your system.

|

||||

|

||||

# Contributing

|

||||

|

||||

Check out the [contribution guide](CONTRIBUTING.md)

|

||||

|

||||

# Acknowledgements

|

||||

|

||||

Thanks to Gian Marti, Thomas Kramer and Thomas E. Benz for implementing the PLIC.

|

||||

|

|

|

|||

|

|

@ -1,8 +1,9 @@

|

|||

bootrom_img = bootrom.img

|

||||

bootrom_img = bootrom.img bootrom.sv

|

||||

|

||||

GCC=riscv64-unknown-elf-gcc

|

||||

OBJCOPY=riscv64-unknown-elf-objcopy

|

||||

DTB=ariane.dtb

|

||||

PYTHON=python

|

||||

|

||||

all: $(bootrom_img)

|

||||

|

||||

|

|

@ -18,5 +19,8 @@ all: $(bootrom_img)

|

|||

%.dtb: %.dts

|

||||

dtc -I dts $< -O dtb -o $@

|

||||

|

||||

%.sv: %.img

|

||||

$(PYTHON) ./gen_rom.py $<

|

||||

|

||||

clean:

|

||||

rm $(bootrom_img) $(DTB)

|

||||

|

|

|

|||

|

|

@ -5,18 +5,23 @@

|

|||

#size-cells = <2>;

|

||||

compatible = "eth,ariane-bare-dev";

|

||||

model = "eth,ariane-bare";

|

||||

// chosen {

|

||||

// stdout-path = "/soc/uart@10000000:115200";

|

||||

// };

|

||||

cpus {

|

||||

#address-cells = <1>;

|

||||

#size-cells = <0>;

|

||||

timebase-frequency = <10000000>;

|

||||

timebase-frequency = <32768>; // 32.768 kHz

|

||||

CPU0: cpu@0 {

|

||||

clock-frequency = <50000000>; // 50 MHz

|

||||

device_type = "cpu";

|

||||

reg = <0>;

|

||||

status = "okay";

|

||||

compatible = "riscv";

|

||||

riscv,isa = "rv64imc";

|

||||

compatible = "eth, ariane", "riscv";

|

||||

riscv,isa = "rv64imacsu";

|

||||

mmu-type = "riscv,sv39";

|

||||

clock-frequency = <1000000000>;

|

||||

tlb-split;

|

||||

// HLIC - hart local interrupt controller

|

||||

CPU0_intc: interrupt-controller {

|

||||

#interrupt-cells = <1>;

|

||||

interrupt-controller;

|

||||

|

|

@ -26,7 +31,7 @@

|

|||

};

|

||||

memory@80000000 {

|

||||

device_type = "memory";

|

||||

reg = <0x0 0x80000000 0x0 0x1000000>;

|

||||

reg = <0x0 0x80000000 0x0 0x1800000>;

|

||||

};

|

||||

soc {

|

||||

#address-cells = <2>;

|

||||

|

|

@ -35,11 +40,35 @@

|

|||

ranges;

|

||||

clint@2000000 {

|

||||

compatible = "riscv,clint0";

|

||||

interrupts-extended = <&CPU0_intc 3 &CPU0_intc 7 >;

|

||||

interrupts-extended = <&CPU0_intc 3 &CPU0_intc 7>;

|

||||

reg = <0x0 0x2000000 0x0 0xc0000>;

|

||||

reg-names = "control";

|

||||

};

|

||||

PLIC0: interrupt-controller@c000000 {

|

||||

#address-cells = <0>;

|

||||

#interrupt-cells = <1>;

|

||||

compatible = "sifive,plic-1.0.0", "riscv,plic0";

|

||||

interrupt-controller;

|

||||

interrupts-extended = <&CPU0_intc 11 &CPU0_intc 9>;

|

||||

reg = <0x0 0xc000000 0x0 0x4000000>;

|

||||

riscv,max-priority = <7>;

|

||||

riscv,ndev = <2>;

|

||||

};

|

||||

debug-controller@0 {

|

||||

compatible = "riscv,debug-013";

|

||||

interrupts-extended = <&CPU0_intc 65535>;

|

||||

reg = <0x0 0x0 0x0 0x1000>;

|

||||

reg-names = "control";

|

||||

};

|

||||

uart@10000000 {

|

||||

compatible = "ns16750";

|

||||

reg = <0x0 0x10000000 0x0 0x1000>;

|

||||

clock-frequency = <50000000>;

|

||||

current-speed = <115200>;

|

||||

interrupt-parent = <&PLIC0>;

|

||||

interrupts = <1>;

|

||||

reg-shift = <2>; // regs are spaced on 32 bit boundary

|

||||

reg-io-width = <4>; // only 32-bit access are supported

|

||||

};

|

||||

};

|

||||

htif {

|

||||

compatible = "ucb,htif0";

|

||||

};

|

||||

};

|

||||

|

|

|

|||

374

bootrom/bootrom.h

Normal file

374

bootrom/bootrom.h

Normal file

|

|

@ -0,0 +1,374 @@

|

|||

// Auto-generated code

|

||||

|

||||

const int reset_vec_size = 368;

|

||||

|

||||

uint32_t reset_vec[reset_vec_size] = {

|

||||

0x0010041b,

|

||||

0x01f41413,

|

||||

0xf1402573,

|

||||

0x00000597,

|

||||

0x07458593,

|

||||

0x00008402,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0xf1402573,

|

||||

0x00000597,

|

||||

0x03c58593,

|

||||

0x10500073,

|

||||

0x0000bff5,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0xedfe0dd0,

|

||||

0x3d050000,

|

||||

0x38000000,

|

||||

0x3c040000,

|

||||

0x28000000,

|

||||

0x11000000,

|

||||

0x10000000,

|

||||

0x00000000,

|

||||

0x01010000,

|

||||

0x04040000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x01000000,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x00000000,

|

||||

0x02000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x0f000000,

|

||||

0x02000000,

|

||||

0x03000000,

|

||||

0x14000000,

|

||||

0x1b000000,

|

||||

0x2c687465,

|

||||

0x61697261,

|

||||

0x622d656e,

|

||||

0x2d657261,

|

||||

0x00766564,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x26000000,

|

||||

0x2c687465,

|

||||

0x61697261,

|

||||

0x622d656e,

|

||||

0x00657261,

|

||||

0x01000000,

|

||||

0x73757063,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x00000000,

|

||||

0x01000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x0f000000,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x2c000000,

|

||||

0x00800000,

|

||||

0x01000000,

|

||||

0x40757063,

|

||||

0x00000030,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x3f000000,

|

||||

0x80f0fa02,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x4f000000,

|

||||

0x00757063,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x5b000000,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x05000000,

|

||||

0x5f000000,

|

||||

0x79616b6f,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x12000000,

|

||||

0x1b000000,

|

||||

0x2c687465,

|

||||

0x69726120,

|

||||

0x00656e61,

|

||||

0x63736972,

|

||||

0x00000076,

|

||||

0x03000000,

|

||||

0x0b000000,

|

||||

0x66000000,

|

||||

0x34367672,

|

||||

0x63616d69,

|

||||

0x00007573,

|

||||

0x03000000,

|

||||

0x0b000000,

|

||||

0x70000000,

|

||||

0x63736972,

|

||||

0x76732c76,

|

||||

0x00003933,

|

||||

0x03000000,

|

||||

0x00000000,

|

||||

0x79000000,

|

||||

0x01000000,

|

||||

0x65746e69,

|

||||

0x70757272,

|

||||

0x6f632d74,

|

||||

0x6f72746e,

|

||||

0x72656c6c,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x83000000,

|

||||

0x01000000,

|

||||

0x03000000,

|

||||

0x00000000,

|

||||

0x94000000,

|

||||

0x03000000,

|

||||

0x0f000000,

|

||||

0x1b000000,

|

||||

0x63736972,

|

||||

0x70632c76,

|

||||

0x6e692d75,

|

||||

0x00006374,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0xa9000000,

|

||||

0x01000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0xaf000000,

|

||||

0x01000000,

|

||||

0x02000000,

|

||||

0x02000000,

|

||||

0x02000000,

|

||||

0x01000000,

|

||||

0x6f6d656d,

|

||||

0x38407972,

|

||||

0x30303030,

|

||||

0x00303030,

|

||||

0x03000000,

|

||||

0x07000000,

|

||||

0x4f000000,

|

||||

0x6f6d656d,

|

||||

0x00007972,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x5b000000,

|

||||

0x00000000,

|

||||

0x00000080,

|

||||

0x00000000,

|

||||

0x00008001,

|

||||

0x02000000,

|

||||

0x01000000,

|

||||

0x00636f73,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x00000000,

|

||||

0x02000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x0f000000,

|

||||

0x02000000,

|

||||

0x03000000,

|

||||

0x1f000000,

|

||||

0x1b000000,

|

||||

0x2c687465,

|

||||

0x61697261,

|

||||

0x622d656e,

|

||||

0x2d657261,

|

||||

0x00636f73,

|

||||

0x706d6973,

|

||||

0x622d656c,

|

||||

0x00007375,

|

||||

0x03000000,

|

||||

0x00000000,

|

||||

0xb7000000,

|

||||

0x01000000,

|

||||

0x6e696c63,

|

||||

0x30324074,

|

||||

0x30303030,

|

||||

0x00000030,

|

||||

0x03000000,

|

||||

0x0d000000,

|

||||

0x1b000000,

|

||||

0x63736972,

|

||||

0x6c632c76,

|

||||

0x30746e69,

|

||||

0x00000000,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0xbe000000,

|

||||

0x01000000,

|

||||

0x03000000,

|

||||

0x01000000,

|

||||

0x07000000,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x5b000000,

|

||||

0x00000000,

|

||||

0x00000002,

|

||||

0x00000000,

|

||||

0x00000c00,

|

||||

0x03000000,

|

||||

0x08000000,

|

||||

0xd2000000,

|

||||

0x746e6f63,

|

||||

0x006c6f72,

|

||||

0x02000000,

|

||||

0x01000000,

|

||||

0x75626564,

|

||||

0x6f632d67,

|

||||

0x6f72746e,

|

||||

0x72656c6c,

|

||||

0x00003040,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x1b000000,

|

||||

0x63736972,

|

||||

0x65642c76,

|

||||

0x2d677562,

|

||||

0x00333130,

|

||||

0x03000000,

|

||||

0x08000000,

|

||||

0xbe000000,

|

||||

0x01000000,

|

||||

0xffff0000,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x5b000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00000000,

|

||||

0x00100000,

|

||||

0x03000000,

|

||||

0x08000000,

|

||||

0xd2000000,

|

||||

0x746e6f63,

|

||||

0x006c6f72,

|

||||

0x02000000,

|

||||

0x01000000,

|

||||

0x74726175,

|

||||

0x30303140,

|

||||

0x30303030,

|

||||

0x00000030,

|

||||

0x03000000,

|

||||

0x08000000,

|

||||

0x1b000000,

|

||||

0x3631736e,

|

||||

0x00303537,

|

||||

0x03000000,

|

||||

0x10000000,

|

||||

0x5b000000,

|

||||

0x00000000,

|

||||

0x00000010,

|

||||

0x00000000,

|

||||

0x00100000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0x3f000000,

|

||||

0x80f0fa02,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0xdc000000,

|

||||

0x00c20100,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0xea000000,

|

||||

0x02000000,

|

||||

0x03000000,

|

||||

0x04000000,

|

||||

0xf4000000,

|

||||

0x04000000,

|

||||

0x02000000,

|

||||

0x02000000,

|

||||

0x02000000,

|

||||

0x09000000,

|

||||

0x64646123,

|

||||

0x73736572,

|

||||

0x6c65632d,

|

||||

0x2300736c,

|

||||

0x657a6973,

|

||||

0x6c65632d,

|

||||

0x6300736c,

|

||||

0x61706d6f,

|

||||

0x6c626974,

|

||||

0x6f6d0065,

|

||||

0x006c6564,

|

||||

0x656d6974,

|

||||

0x65736162,

|

||||

0x6572662d,

|

||||

0x6e657571,

|

||||

0x63007963,

|

||||

0x6b636f6c,

|

||||

0x6572662d,

|

||||

0x6e657571,

|

||||

0x64007963,

|

||||

0x63697665,

|

||||

0x79745f65,

|

||||

0x72006570,

|

||||

0x73006765,

|

||||

0x75746174,

|

||||

0x69720073,

|

||||

0x2c766373,

|

||||

0x00617369,

|

||||

0x2d756d6d,

|

||||

0x65707974,

|

||||

0x626c7400,

|

||||

0x6c70732d,

|

||||

0x23007469,

|

||||

0x65746e69,

|

||||

0x70757272,

|

||||

0x65632d74,

|

||||

0x00736c6c,

|

||||

0x65746e69,

|

||||

0x70757272,

|

||||

0x6f632d74,

|

||||

0x6f72746e,

|

||||

0x72656c6c,

|

||||

0x6e696c00,

|

||||

0x702c7875,

|

||||

0x646e6168,

|

||||

0x7200656c,

|

||||

0x65676e61,

|

||||

0x6e690073,

|

||||

0x72726574,

|

||||

0x73747075,

|

||||

0x7478652d,

|

||||

0x65646e65,

|

||||

0x65720064,

|

||||

0x616e2d67,

|

||||

0x0073656d,

|

||||

0x72727563,

|

||||

0x2d746e65,

|

||||

0x65657073,

|

||||

0x65720064,

|

||||

0x68732d67,

|

||||

0x00746669,

|

||||

0x2d676572,

|

||||

0x772d6f69,

|

||||

0x68746469,

|

||||

0x00000000

|

||||

};

|

||||

Binary file not shown.

|

|

@ -20,150 +20,193 @@ module bootrom (

|

|||

input logic [63:0] addr_i,

|

||||

output logic [63:0] rdata_o

|

||||

);

|

||||

localparam int RomSize = 141;

|

||||

localparam int RomSize = 184;

|

||||

|

||||

const logic [RomSize-1:0][63:0] mem = {

|

||||

64'h00000000_00000064,

|

||||

64'h65646E65_7478652D,

|

||||

64'h73747075_72726574,

|

||||

64'h6E690073_65676E61,

|

||||

64'h7200656C_646E6168,

|

||||

64'h70007265_6C6C6F72,

|

||||

64'h746E6F63_2D747075,

|

||||

64'h72726574_6E690073,

|

||||

64'h6C6C6563_2D747075,

|

||||

64'h72726574_6E692300,

|

||||

64'h79636E65_75716572,

|

||||

64'h662D6B63_6F6C6300,

|

||||

64'h65707974_2D756D6D,

|

||||

64'h00617369_2C766373,

|

||||

64'h69720073_75746174,

|

||||

64'h73006765_72006570,

|

||||

64'h79745F65_63697665,

|

||||

64'h64007963_6E657571,

|

||||

64'h6572662D_65736162,

|

||||

64'h656D6974_006C6564,

|

||||

64'h6F6D0065_6C626974,

|

||||

64'h61706D6F_6300736C,

|

||||

64'h6C65632D_657A6973,

|

||||

64'h2300736C_6C65632D,

|

||||

64'h73736572_64646123,

|

||||

64'h09000000_02000000,

|

||||

64'h02000000_00000030,

|

||||

64'h66697468_2C626375,

|

||||

64'h1B000000_0A000000,

|

||||

64'h03000000_00000000,

|

||||

64'h66697468_01000000,

|

||||

64'h00000000_68746469,

|

||||

64'h772d6f69_2d676572,

|

||||

64'h00746669_68732d67,

|

||||

64'h65720064_65657073,

|

||||

64'h2d746e65_72727563,

|

||||

64'h0073656d_616e2d67,

|

||||

64'h65720064_65646e65,

|

||||

64'h7478652d_73747075,

|

||||

64'h72726574_6e690073,

|

||||

64'h65676e61_7200656c,

|

||||

64'h646e6168_702c7875,

|

||||

64'h6e696c00_72656c6c,

|

||||

64'h6f72746e_6f632d74,

|

||||

64'h70757272_65746e69,

|

||||

64'h00736c6c_65632d74,

|

||||

64'h70757272_65746e69,

|

||||

64'h23007469_6c70732d,

|

||||

64'h626c7400_65707974,

|

||||

64'h2d756d6d_00617369,

|

||||

64'h2c766373_69720073,

|

||||

64'h75746174_73006765,

|

||||

64'h72006570_79745f65,

|

||||

64'h63697665_64007963,

|

||||

64'h6e657571_6572662d,

|

||||

64'h6b636f6c_63007963,

|

||||

64'h6e657571_6572662d,

|

||||

64'h65736162_656d6974,

|

||||

64'h006c6564_6f6d0065,

|

||||

64'h6c626974_61706d6f,

|

||||

64'h6300736c_6c65632d,

|

||||

64'h657a6973_2300736c,

|

||||

64'h6c65632d_73736572,

|

||||

64'h64646123_09000000,

|

||||

64'h02000000_02000000,

|

||||

64'h00000C00_00000000,

|

||||

64'h00000002_00000000,

|

||||

64'h4B000000_10000000,

|

||||

64'h03000000_07000000,

|

||||

64'h01000000_03000000,

|

||||

64'h01000000_AE000000,

|

||||

64'h02000000_04000000,

|

||||

64'hf4000000_04000000,

|

||||

64'h03000000_02000000,

|

||||

64'hea000000_04000000,

|

||||

64'h03000000_00c20100,

|

||||

64'hdc000000_04000000,

|

||||

64'h03000000_80f0fa02,

|

||||

64'h3f000000_04000000,

|

||||

64'h03000000_00100000,

|

||||

64'h00000000_00000010,

|

||||

64'h00000000_5b000000,

|

||||

64'h10000000_03000000,

|

||||

64'h00000000_30746E69,

|

||||

64'h6C632C76_63736972,

|

||||

64'h1B000000_0D000000,

|

||||

64'h00303537_3631736e,

|

||||

64'h1b000000_08000000,

|

||||

64'h03000000_00000030,

|

||||

64'h30303030_30324074,

|

||||

64'h6E696C63_01000000,

|

||||

64'hA7000000_00000000,

|

||||

64'h03000000_00007375,

|

||||

64'h622D656C_706D6973,

|

||||

64'h00636F73_2D657261,

|

||||

64'h622D656E_61697261,

|

||||

64'h2C687465_1B000000,

|

||||

64'h1F000000_03000000,

|

||||

64'h02000000_0F000000,

|

||||

64'h04000000_03000000,

|

||||

64'h02000000_00000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00636F73_01000000,

|

||||

64'h02000000_00000001,

|

||||

64'h00000000_00000080,

|

||||

64'h00000000_4B000000,

|

||||

64'h30303030_30303140,

|

||||

64'h74726175_01000000,

|

||||

64'h02000000_006c6f72,

|

||||

64'h746e6f63_d2000000,

|

||||

64'h08000000_03000000,

|

||||

64'h00100000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h5b000000_10000000,

|

||||

64'h03000000_ffff0000,

|

||||

64'h01000000_be000000,

|

||||

64'h08000000_03000000,

|

||||

64'h00333130_2d677562,

|

||||

64'h65642c76_63736972,

|

||||

64'h1b000000_10000000,

|

||||

64'h03000000_00003040,

|

||||

64'h72656c6c_6f72746e,

|

||||

64'h6f632d67_75626564,

|

||||

64'h01000000_02000000,

|

||||

64'h006c6f72_746e6f63,

|

||||

64'hd2000000_08000000,

|

||||

64'h03000000_00000c00,

|

||||

64'h00000000_00000002,

|

||||

64'h00000000_5b000000,

|

||||

64'h10000000_03000000,

|

||||

64'h00007972_6F6D656D,

|

||||

64'h3F000000_07000000,

|

||||

64'h03000000_00303030,

|

||||

64'h30303030_38407972,

|

||||

64'h6F6D656D_01000000,

|

||||

64'h02000000_02000000,

|

||||

64'h02000000_01000000,

|

||||

64'h9F000000_04000000,

|

||||

64'h03000000_00006374,

|

||||

64'h6E692D75_70632C76,

|

||||

64'h63736972_1B000000,

|

||||

64'h0F000000_03000000,

|

||||

64'h8A000000_00000000,

|

||||

64'h07000000_01000000,

|

||||

64'h03000000_01000000,

|

||||

64'h79000000_04000000,

|

||||

64'hbe000000_10000000,

|

||||

64'h03000000_00000000,

|

||||

64'h72656C6C_6F72746E,

|

||||

64'h6F632D74_70757272,

|

||||

64'h65746E69_01000000,

|

||||

64'h00CA9A3B_69000000,

|

||||

64'h30746e69_6c632c76,

|

||||

64'h63736972_1b000000,

|

||||

64'h0d000000_03000000,

|

||||

64'h00000030_30303030,

|

||||

64'h30324074_6e696c63,

|

||||

64'h01000000_b7000000,

|

||||

64'h00000000_03000000,

|

||||

64'h00007375_622d656c,

|

||||

64'h706d6973_00636f73,

|

||||

64'h2d657261_622d656e,

|

||||

64'h61697261_2c687465,

|

||||

64'h1b000000_1f000000,

|

||||

64'h03000000_02000000,

|

||||

64'h0f000000_04000000,

|

||||

64'h03000000_02000000,

|

||||

64'h00000000_04000000,

|

||||

64'h03000000_00636f73,

|

||||

64'h01000000_02000000,

|

||||

64'h00008001_00000000,

|

||||

64'h00000080_00000000,

|

||||

64'h5b000000_10000000,

|

||||

64'h03000000_00007972,

|

||||

64'h6f6d656d_4f000000,

|

||||

64'h07000000_03000000,

|

||||

64'h00303030_30303030,

|

||||

64'h38407972_6f6d656d,

|

||||

64'h01000000_02000000,

|

||||

64'h02000000_02000000,

|

||||

64'h01000000_af000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00003933_76732C76,

|

||||

64'h63736972_60000000,

|

||||

64'h0B000000_03000000,

|

||||

64'h00636D69_34367672,

|

||||

64'h56000000_08000000,

|

||||

64'h03000000_00000076,

|

||||

64'h63736972_1B000000,

|

||||

64'h06000000_03000000,

|

||||

64'h00000000_79616B6F,

|

||||

64'h4F000000_05000000,

|

||||

64'h01000000_a9000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00006374_6e692d75,

|

||||

64'h70632c76_63736972,

|

||||

64'h1b000000_0f000000,

|

||||

64'h03000000_94000000,

|

||||

64'h00000000_03000000,

|

||||

64'h01000000_83000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00000000_72656c6c,

|

||||

64'h6f72746e_6f632d74,

|

||||

64'h70757272_65746e69,

|

||||

64'h01000000_79000000,

|

||||

64'h00000000_03000000,

|

||||

64'h00003933_76732c76,

|

||||

64'h63736972_70000000,

|

||||

64'h0b000000_03000000,

|

||||

64'h00007573_63616d69,

|

||||

64'h34367672_66000000,

|

||||

64'h0b000000_03000000,

|

||||

64'h00000076_63736972,

|

||||

64'h00656e61_69726120,

|

||||

64'h2c687465_1b000000,

|

||||

64'h12000000_03000000,

|

||||

64'h00000000_79616b6f,

|

||||

64'h5f000000_05000000,

|

||||

64'h03000000_00000000,

|

||||

64'h4B000000_04000000,

|

||||

64'h5b000000_04000000,

|

||||

64'h03000000_00757063,

|

||||

64'h3F000000_04000000,

|

||||

64'h4f000000_04000000,

|

||||

64'h03000000_80f0fa02,

|

||||

64'h3f000000_04000000,

|

||||

64'h03000000_00000030,

|

||||

64'h40757063_01000000,

|

||||

64'h80969800_2C000000,

|

||||

64'h00800000_2c000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00000000_0F000000,

|

||||

64'h00000000_0f000000,

|

||||

64'h04000000_03000000,

|

||||

64'h01000000_00000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00000000_73757063,

|

||||

64'h01000000_00657261,

|

||||

64'h622D656E_61697261,

|

||||

64'h2C687465_26000000,

|

||||

64'h622d656e_61697261,

|

||||

64'h2c687465_26000000,

|

||||

64'h10000000_03000000,

|

||||

64'h00766564_2D657261,

|

||||

64'h622D656E_61697261,

|

||||

64'h2C687465_1B000000,

|

||||

64'h00766564_2d657261,

|

||||

64'h622d656e_61697261,

|

||||

64'h2c687465_1b000000,

|

||||

64'h14000000_03000000,

|

||||

64'h02000000_0F000000,

|

||||

64'h02000000_0f000000,

|

||||

64'h04000000_03000000,

|

||||

64'h02000000_00000000,

|

||||

64'h04000000_03000000,

|

||||

64'h00000000_01000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'hE8020000_C2000000,

|

||||

64'h04040000_01010000,

|

||||

64'h00000000_10000000,

|

||||

64'h11000000_28000000,

|

||||

64'h20030000_38000000,

|

||||

64'hE2030000_EDFE0DD0,

|

||||

64'h3c040000_38000000,

|

||||

64'h3d050000_edfe0dd0,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_0000BFF5,

|

||||

64'h10500073_03C58593,

|

||||

64'h00000597_F1402573,

|

||||

64'h00000000_0000bff5,

|

||||

64'h10500073_03c58593,

|

||||

64'h00000597_f1402573,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00000000_00000000,

|

||||

64'h00008402_07458593,

|

||||

64'h00000597_F1402573,

|

||||

64'h01F41413_0010041B

|

||||

64'h00000597_f1402573,

|

||||

64'h01f41413_0010041b

|

||||

};

|

||||

|

||||

logic [$clog2(RomSize)-1:0] addr_q;

|

||||

|

|

@ -174,7 +217,7 @@ module bootrom (

|

|||

end

|

||||

end

|

||||

|

||||

// this prevents spurious Xes from propagating into

|

||||

// this prevents spurious Xes from propagating into

|

||||

// the speculative fetch stage of the core

|

||||

assign rdata_o = (addr_q<RomSize) ? mem[addr_q] : '0;

|

||||

assign rdata_o = (addr_q < RomSize) ? mem[addr_q] : '0;

|

||||

endmodule

|

||||

|

|

|

|||

|

|

@ -4,6 +4,7 @@ from string import Template

|

|||

import argparse

|

||||

import os.path

|

||||

import sys

|

||||

from bitstring import ConstBitStream, BitArray, BitStream

|

||||

|

||||

parser = argparse.ArgumentParser(description='Convert binary file to verilog rom')

|

||||

parser.add_argument('filename', metavar='filename', nargs=1,

|

||||

|

|

@ -48,7 +49,7 @@ module $filename (

|

|||

localparam int RomSize = $size;

|

||||

|

||||

const logic [RomSize-1:0][63:0] mem = {

|

||||

$content

|

||||

$content

|

||||

};

|

||||

|

||||

logic [$$clog2(RomSize)-1:0] addr_q;

|

||||

|

|

@ -59,56 +60,69 @@ module $filename (

|

|||

end

|

||||

end

|

||||

|

||||

// this prevents spurious Xes from propagating into

|

||||

// this prevents spurious Xes from propagating into

|

||||

// the speculative fetch stage of the core

|

||||

assign rdata_o = (addr_q<RomSize) ? mem[addr_q] : '0;

|

||||

assign rdata_o = (addr_q < RomSize) ? mem[addr_q] : '0;

|

||||

endmodule

|

||||

"""

|

||||

|

||||

rom = []

|

||||

c_var = """\

|

||||

// Auto-generated code

|

||||

|

||||

with open(filename + ".img", "rb") as f:

|

||||

byte = True;

|

||||

while byte:

|

||||

word = ""

|

||||

# read 64-bit a.k.a 8 byte

|

||||

for i in range(0, 8):

|

||||

byte = f.read(1)

|

||||

if i == 4:

|

||||

word = "_" + word

|

||||

if byte:

|

||||

word = ("%02X" % int.from_bytes(byte, "little")) + word

|

||||

# fill up with zeros if unaligned

|

||||

else:

|

||||

pass

|

||||

word = "00" + word;

|

||||

const int reset_vec_size = $size;

|

||||

|

||||

uint32_t reset_vec[reset_vec_size] = {

|

||||

$content

|

||||

};

|

||||

"""

|

||||

|

||||

def read_bin():

|

||||

s = ConstBitStream(filename=filename + ".img")

|

||||

rom = []

|

||||

try:

|

||||

while True:

|

||||

rom.append(s.read("hex:8"))

|

||||

except Exception as e:

|

||||

pass

|

||||

|

||||

# align to 64 bit

|

||||

align = (int(len(rom) / 8) + 1) * 8;

|

||||

|

||||

for i in range(len(rom), align):

|

||||

rom.append("00")

|

||||

|

||||

return rom

|

||||

|

||||

rom = read_bin()

|

||||

|

||||

""" Generate C header file for simulator

|

||||

"""

|

||||

with open(filename + ".h", "w") as f:

|

||||

rom_str = ""

|

||||

# process in junks of 32 bit (4 byte)

|

||||

for i in range(0, int(len(rom)/4)):

|

||||

rom_str += " 0x" + "".join(rom[i*4:i*4+4][::-1]) + ",\n"

|

||||

|

||||

# remove the trailing comma

|

||||

rom_str = rom_str[:-2]

|

||||

|

||||

s = Template(c_var)

|

||||

f.write(s.substitute(filename=filename, size=int(len(rom)/4), content=rom_str))

|

||||

|

||||

if word != "_":

|

||||

word = "64'h" + word

|

||||

# print(word)

|

||||

rom.append(word)

|

||||

f.close()

|

||||

|

||||

|

||||

rom.reverse()

|

||||

|

||||

# open file for writing

|

||||

""" Generate SystemVerilog bootcode for FPGA and ASIC

|

||||

"""

|

||||

with open(filename + ".sv", "w") as f:

|

||||

|

||||

# some string preparations

|

||||

rom_str = ""

|

||||

i = 0

|

||||

for r in rom:

|

||||

i += 1

|

||||

rom_str += r + ",\n ";

|

||||

# process in junks of 64 bit (8 byte)

|

||||

for i in reversed(range(int(len(rom)/8))):

|

||||

rom_str += " 64'h" + "".join(rom[i*8+4:i*8+8][::-1]) + "_" + "".join(rom[i*8:i*8+4][::-1]) + ",\n"

|

||||

|

||||

rom_str.rstrip()

|

||||

# strip the last whitespace

|

||||

rom_str = rom_str[:-10]

|

||||

# remove the trailing comma

|

||||

rom_str = rom_str[:-2]

|

||||

|

||||

# write files

|

||||

f.write(license)

|

||||

s = Template(module)

|

||||

f.write(s.substitute(filename=filename, size=i, content=rom_str))

|

||||

f.write(s.substitute(filename=filename, size=int(len(rom)/8), content=rom_str))

|

||||

|

||||

f.close()

|

||||

|

|

|

|||

|

|

@ -1,7 +1,7 @@

|

|||

#!/bin/bash

|

||||

set -e

|

||||

ROOT=$(cd "$(dirname "${BASH_SOURCE[0]}")/.." && pwd)

|

||||

VERSION="294bfce8a1ca2fc501b8939292146e44f813a2b8"

|

||||

VERSION="7cc76ea83b4f827596158c8ba0763e93da65de8f"

|

||||

|

||||

cd $ROOT/tmp

|

||||

|

||||

|

|

|

|||

|

|

@ -46,7 +46,7 @@ torture.testrun.dump false

|

|||

torture.testrun.vec false

|

||||

|

||||

torture.overnight.errors 1

|

||||

torture.overnight.minutes 1

|

||||

torture.overnight.minutes 100000

|

||||

torture.overnight.outdir output/failedtests

|

||||

torture.overnight.email your@email.address

|

||||

|

||||

|

|

|

|||

10

failedtests/.gitignore

vendored

10

failedtests/.gitignore

vendored

|

|

@ -1,10 +0,0 @@

|

|||

# Ignore all

|

||||

*

|

||||

# Unignore all with extensions

|

||||

!*.*

|

||||

# Ignore files with specific extension

|

||||

*.hex

|

||||

*.dump

|

||||

*.sig

|

||||

*.stats

|

||||

*.dasm

|

||||

|

|

@ -1,72 +0,0 @@

|

|||

#=======================================================================

|

||||

# UCB VLSI FLOW: Makefile for riscv-tests

|

||||

#-----------------------------------------------------------------------

|

||||

# Yunsup Lee (yunsup@cs.berkeley.edu)

|

||||

#

|

||||

|

||||

default: all

|

||||

|

||||

#--------------------------------------------------------------------

|

||||

# Sources

|

||||

#--------------------------------------------------------------------

|

||||

|

||||

asm_tests = $(wildcard *.S)

|

||||

|

||||

extra_files =

|

||||

|

||||

#--------------------------------------------------------------------

|

||||

# Build rules

|

||||

#--------------------------------------------------------------------

|

||||

|

||||

RISCV_GCC = riscv64-unknown-elf-gcc

|

||||

RISCV_GCC_OPTS = -nostdlib -nostartfiles -Wa,-march=rv64i

|

||||

RISCV_OBJCOPY ?= $(RISCV_PREFIX)objcopy

|

||||

RISCV_OBJDUMP = riscv64-unknown-elf-objdump --disassemble-all --section=.text --section=.data --section=.bss

|

||||

RISCV_SIM = spike

|

||||

|

||||

#------------------------------------------------------------

|

||||

# Build assembly tests

|

||||

|

||||

asm_tests_bin = $(patsubst %.S, %, $(asm_tests))

|

||||

asm_tests_verilog = $(addsuffix .v, $(asm_tests_bin))

|

||||

asm_tests_dump = $(addsuffix .dump, $(asm_tests_bin))

|

||||

asm_tests_sig = $(addsuffix .sig, $(asm_tests_bin))

|

||||

asm_tests_hex = $(addsuffix .hex, $(asm_tests_bin))

|

||||

|

||||

$(asm_tests_dump): %.dump: %

|

||||

$(RISCV_OBJDUMP) $< > $@

|

||||

|

||||

$(asm_tests_verilog): %.v: %

|

||||

$(RISCV_OBJCOPY) -O verilog $< $@

|

||||

|

||||

$(asm_tests_bin): %: %.S $(extra_files)

|

||||

$(RISCV_GCC) $(RISCV_GCC_OPTS) -I../riscv-torture/env/p -T../riscv-torture/env/p/link.ld $< -o $@

|

||||

|

||||

$(asm_tests_hex): %.hex: % $(extra_files)

|

||||

elf2hex 8 16384 $< 2147483648 > $@

|

||||

|

||||

$(asm_tests_sig): %.sig: %

|

||||

$(RISCV_SIM) +signature=$@ $<

|

||||

|

||||

new:

|

||||

cd ..; make gen

|

||||

|

||||

run: $(asm_tests_sig)

|

||||

echo; perl -ne 'print " [$$1] $$ARGV \t$$2\n" if /\*{3}(.{8})\*{3}(.*)/' \

|

||||

$(asm_tests_sig); echo;

|

||||

|

||||

junk += $(asm_tests_bin) $(asm_tests_dump) $(asm_tests_sig) $(asm_tests_hex)

|

||||

|

||||

#------------------------------------------------------------

|

||||

# Default

|

||||

|

||||

all: $(asm_tests_dump) $(asm_tests_hex)

|

||||

|

||||

#------------------------------------------------------------

|

||||

# Clean up

|

||||

|

||||

clean:

|

||||

rm -rf $(junk)

|

||||

|

||||

clean-all: clean

|

||||

rm -rf test*.S test*.stats test*.hex test*.out test*.dump test test_1* test_pseg_* schad* failedtests/*

|

||||

|

|

@ -1,10 +0,0 @@

|

|||

# Failed Test Report

|

||||

|

||||

## VMA Tests

|

||||

|

||||

* test_1498676631701:

|

||||

* Found bug in misaligned exception of half word access when another LSU request was incoming

|

||||

|

||||

* test_1498880354372:

|

||||

* Found bug in `sfence.vma`, pipeline wasn't flushing due to wrong assignment on the no store pending signal, coming from the store buffer

|

||||

* Found bug in accidental exception taken in the MMU: Even though the LSU didn't place a request on the MMU the MMU was propagating a misaligned exception signal. The solution was masking it by the `lsu_req` signal.

|

||||

|

|

@ -1,742 +0,0 @@

|

|||

// random assembly code generated by RISC-V torture test generator

|

||||

// nseqs = 200

|

||||

// memsize = 1024

|

||||

|

||||

#include "riscv_test.h"

|

||||

|

||||

RVTEST_RV64U

|

||||

RVTEST_CODE_BEGIN

|

||||

|

||||

j test_start

|

||||

|