- VHDL 49.2%

- C 44.5%

- Makefile 2.3%

- Tcl 1.1%

- Python 0.7%

- Other 2.1%

|

Some checks are pending

Build Documentation / API Documentation (push) Waiting to run

Build Documentation / Datasheet & User Guide (push) Waiting to run

Build Documentation / Deploy to Releases and Pages (push) Blocked by required conditions

Processor Check / processor simulation (push) Waiting to run

Processor Check / processor simulation-1 (push) Waiting to run

Verilog Conversion / ♻️ Convert to Verilog (push) Waiting to run

Verilog Conversion / 🖥️ Verilog simulation - Icarus Verilog (push) Blocked by required conditions

Verilog Conversion / 🖥️ Verilog simulation - Verilator (push) Blocked by required conditions

|

||

|---|---|---|

| .github | ||

| docs | ||

| rtl | ||

| sim | ||

| sw | ||

| .gitattributes | ||

| .gitignore | ||

| .gitmodules | ||

| CHANGELOG.md | ||

| CODE_OF_CONDUCT.md | ||

| CONTRIBUTING.md | ||

| LICENSE | ||

| README.md | ||

The NEORV32 RISC-V Processor

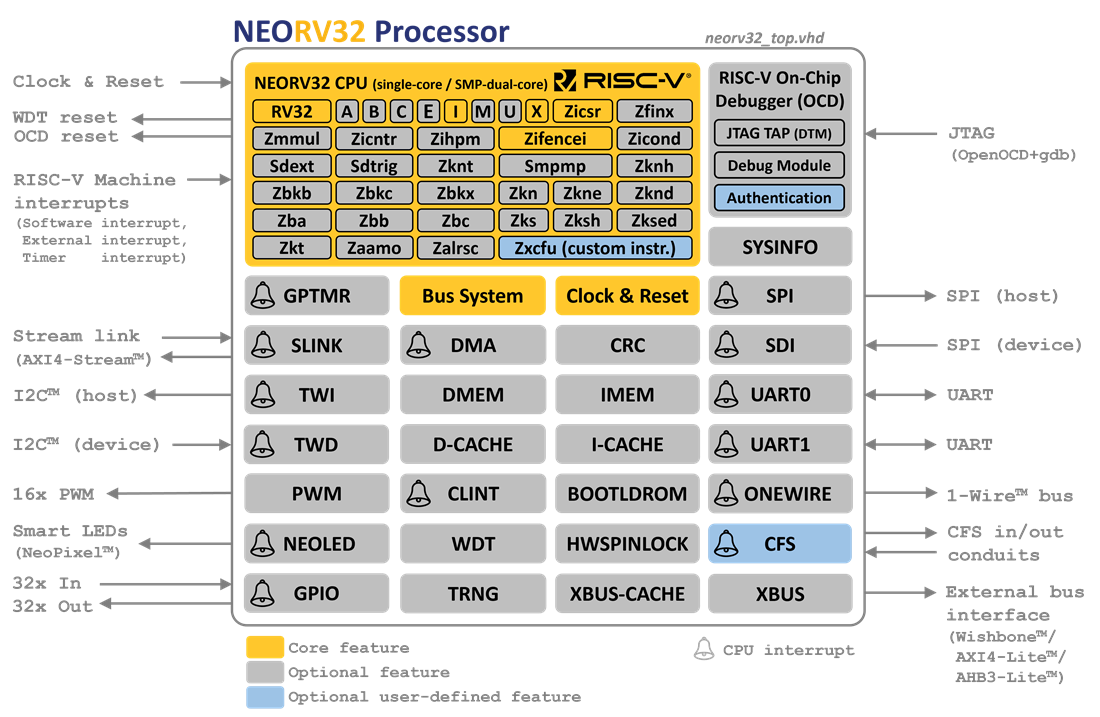

The NEORV32 Processor is a customizable microcontroller-like system on chip (SoC) built around the NEORV32 RISC-V CPU that is written in platform-independent VHDL. The processor is intended as auxiliary controller in larger SoC designs or as tiny and customized microcontroller. The project is intended to work out of the box and targets FPGA / RISC-V beginners as well as experienced users.

Key Features

- all-in-one package: CPU + SoC + Software Framework + Test Infrastructure

- fully self-contained - no external source dependencies

- completely described in behavioral, platform-independent VHDL - no primitives, macros, attributes, etc.

- technology friendly; e.g. all internal memories can be mapped to FPGA or ASIC primitives

- extensive CPU & SoC configuration options for adapting to application requirements

- aims to be as small as possible while being as RISC-V-compliant as possible

- optimized for high clock frequencies to ease integration and timing closure

- from zero to

printf("hello world");- completely open-source and documented - easy to use – intended to work out of the box

- ♻️ Looking for an all-Verilog version? Have a look at the auto-conversion setup.

- 🔍 Continuous integration to check for regressions (including RISC-V ISA compatibility check using RISCOF).

- 📂 Exemplary setups and community projects targeting various FPGA boards and toolchains to get started.

- 📦 The entire processor is also available as Vivado IP Block.

- 🪁 Upstream Zephyr and FreeRTOS operating system support.

- 🐧 Capable of running nommu-Linux.

- 🏗️ LiteX SoC builder integration.

- ⚙️ MicroPython port, Ada support, and Rust integration via Embassy framework.

- 🖥️ Pre-configured Eclipse project for developing and debugging code using an IDE.

- 🏷️ The project's change log is available in CHANGELOG.md.

- 🚀 Check out the quick links below and the User Guide to get started.

- 📚 For detailed information see the online documentation.

Project Status

| Task | CI Status |

|---|---|

| GitHub pages |  |

| Documentation |  |

| Processor check |  |

| Verilog conversion |  |

| RISC-V compatibility |  |

The processor passes the official RISC-V architecture compatibility tests. It can successfully run any C program including CoreMark and FreeRTOS and can be synthesized for any target technology - tested on AMD, Intel, Lattice, Microchip, Gowin and Cologne Chip FPGAs. The processor has also been taped out several times as an ASIC.

Features

The NEORV32 Processor provides a full-featured microcontroller-like SoC build around the NEORV32 CPU. By using generics the design is highly configurable and allows a flexible customization to tailor the setup according to your needs. Note that all of the following SoC modules are entirely optional.

CPU Core(s)

- RISC-V 32-bit little-endian pipelined/multi-cycle modified-Harvard architecture

- Single-core or SMP dual-core configuration

- configurable instruction sets and extensions:

RV32IEMACBUXZaamoZalrscZcbZbaZbbZbkbZbkcZbkxZbsZfinxZibiZicntrZicondZicsrZifenceiZihpmZimopZknZkndZkneZknhZktZksZksedZkshZmmulSdextSdtrigSmcntrpmfSmpmpXcfu - compatible to subsets of the RISC-V "Unprivileged ISA Specification" and "Privileged Architecture Specification"

machineanduserprivilege modes- implements all standard RISC-V exceptions and interrupts + 16 fast interrupt request channels as NEORV32-specific extension

- custom functions unit (CFU as custom

XcfuISA extension) for custom RISC-V instructions

Memories

- tightly-coupled data and instruction memories (DMEM & IMEM) and caches (iCACHE & dCACHE)

- pre-installed bootloader (BOOTLDROM) with serial user interface; allows booting application code via UART, I²C or SPI flash and SD card

Timers and Counters

- RISC-V-compatible core-local interruptor (CLINT)

- 32-bit general purpose timer (GPTMR) with up to 16 individual timer slices

- watchdog timer (WDT)

Input / Output

- standard serial interfaces: 2x UART, SPI (SPI host), SDI (SPI device), TWI (I²C host), TWD (I²C device), ONEWIRE (1-wire host)

- up to 32 general purpose IOs (GPIO, interrupt-capable) and up to 32 individual PWM channels

- smart LED interface (NEOLED) to directly control NeoPixel(TM) LEDs

SoC Connectivity

- 32-bit external bus interface - Wishbone-compatible (XBUS); bridge for AXI4-compatible interfaces

- stream link interface with independent RX and TX channels - AXI4-Stream-compatible (SLINK)

Advanced

- true-random number generator (TRNG) based on the neoTRNG

- custom functions subsystem (CFS) for custom tightly-coupled co-processors, accelerators or interfaces

- direct memory access controller (DMA) for CPU-independent data transfers and conversions

- RVFI-compatible trace port for advanced debugging, profiling or verification

Debugging

- on-chip debugger (OCD) accessible via standard JTAG interface

- compatible to the "Minimal RISC-V Debug Specification Version 1.0"

- compatible with OpenOCD, GDB and Segger Embedded Studio

- RISC-V trigger module for hardware-assisted break- and watchpoints

- optional JTAG authentication module to implement custom security mechanisms

- execution trace buffer (TRACER)

Size ad Performance

The NEORV32 processor is optimized for minimal size. However, the actual size (silicon area or FPGA resources)

depends on the specific configuration. For example, an RTOS-capable setup based on a rv32imc_Zicsr_Zicntr CPU

configuration requires about 2300 LUTs and 1000 FFs and can run at up to 130 MHz (implementation results for an

Altera Cyclone IV E EP4CE22F17C6 FPGA). This configuration provides a CoreMark score of 95.23 (0.9523 CoreMarks/MHz).

More information regarding the CPU performance can be found in the Data Sheet: Performance.

Getting Started

This overview provides some quick links to the most important sections of the online Data Sheet and the online User Guide.

🔍 NEORV32 Project - An Introduction

- Key Features - what makes it special

- Structure - folders, RTL files and compile order

- File-List Files - to simplify HDL setup

- Metrics - FPGA implementation and performance evaluation

- RISC-V Compatibility - what is compatible to the specs and what is not

🖥️ NEORV32 Processor - The SoC

- Top Entity - Signals - how to connect to the processor

- Top Entity - Generics - processor/CPU configuration options

- Address Space - memory layout and address mapping

- Boot Configuration - how to make the processor start executing

- SoC Modules - IO/peripheral modules and memories

- On-Chip Debugger - in-system debugging via JTAG

🧮 NEORV32 CPU - The Core

- Architecture - a look under the hood

- Full Virtualization - execution safety

- ISA and Extensions - available (RISC-V) ISA extensions

- CSRs - control and status registers

- Traps - interrupts and exceptions

💾 Software Framework - The Software Ecosystem

- Example Programs - examples how to use the processor's IO/peripheral modules

- Core Libraries - high-level functions for accessing the processor's peripherals

- Software Framework Documentation - doxygen-based

- Application Makefile - turning your application into an executable

- Bootloader - the build-in NEORV32 bootloader

- Image Generator - create (FPGA) memory initialization files from your application

- Semihosting - access files and system services on the host computer

🚀 User Guide - Getting Started

- Toolchain Setup - install and set up the RISC-V GCC toolchain

- General Hardware Setup - set up a new NEORV32 FPGA project

- Adding Custom Hardware Modules - add your custom hardware

- Convert to Verilog - turn the NEORV32 into an all-Verilog design

- Package as Vivado IP block - turn the entire processor into an interactive AMD Vivado IP block

- Using Eclipse - use the Eclipse IDE for developing and debugging

This is an open-source project that is free of charge and provided under an permissive license. See the legal section for more information.

Contributing

Contributions are very welcome! If you’d like to improve something, fix a bug, or add a feature, feel free to open an issue or submit a pull request. See how to contribute. A big thank you goes out to the community and all contributors who help improve this project: